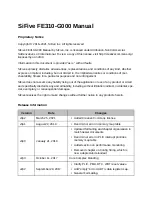

Table 1:

FE310-G000 Feature Summary.

Feature

Description

Available in

QFN48

PWM 1

16-bit Pulse-width modulator with 4 comparators.

✔

PWM 2

16-bit Pulse-width modulator with 4 comparators.

✔

GPIO

32 General Purpose I/O pins.

✔

(19 pins)

Always On

Domain

Supports low-power operation and wakeup.

✔

1.2

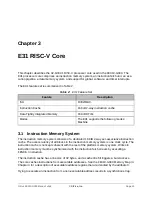

E31 RISC‑V Core

The FE310-G000 includes a 32-bit E31 RISC‑V core, which has a high-performance single-

issue in-order execution pipeline, with a peak sustainable execution rate of one instruction per

clock cycle. The E31 core supports Machine mode only as well as standard Multiply, Atomic,

and Compressed RISC‑V extensions (RV32IMAC).

The core is described in more detail in Chapter 3.

1.3

Interrupts

The FE310-G000 includes a RISC-V standard platform-level interrupt controller (PLIC), which

supports 51 global interrupts with 7 priority levels. The FE310-G000 also provides the standard

RISC‑V machine-mode timer and software interrupts via the Core-Local Interruptor (CLINT).

Interrupts are described in Chapter 8. The CLINT is described in Chapter 9. The PLIC is

described in Chapter 10.

1.4

On-Chip Memory System

The E31 core has a(n) 2-way set-associative 16 KiB L1 instruction cache and a(n) 16 KiB L1

DTIM.

The Level 1 memories are described in Chapter 3.

1.5

Always-On (AON) Block

The AON block contains the reset logic for the chip, an on-chip low-frequency oscillator, a

watchdog timer, connections for an off-chip low-frequency oscillator, the real-time clock, a pro-

grammable power-management unit, and 16×32-bit backup registers that retain state while the

rest of the chip is in a low-power mode.

Chapter 1 Introduction

SiFive FE310-G000 Manual: v3p2

© SiFive, Inc.

Page 10

Содержание FE310-G000

Страница 1: ...SiFive FE310 G000 Manual v3p2 SiFive Inc ...