9.1

CLINT Memory Map

.................................................................................................. 40

9.2

MSIP Registers

......................................................................................................... 41

9.3

Timer Registers

........................................................................................................ 41

10

Platform-Level Interrupt Controller (PLIC)

...........................................42

10.1

Memory Map

.......................................................................................................... 42

10.2

Interrupt Sources

.................................................................................................... 43

10.3

Interrupt Priorities

.................................................................................................... 44

10.4

Interrupt Pending Bits

.............................................................................................. 44

10.5

Interrupt Enables

..................................................................................................... 45

10.6

Priority Thresholds

.................................................................................................. 46

10.7

Interrupt Claim Process

........................................................................................... 47

10.8

Interrupt Completion

................................................................................................ 47

11

One-Time Programmable Memory (OTP) Peripheral

......................49

11.1

Memory Map

.......................................................................................................... 49

11.2

Programmed-I/O lock register (

otp_lock

)

................................................................50

11.3

Programmed-I/O Sequencing

................................................................................... 51

11.4

Read sequencer control register (

otp_rsctrl

)

........................................................51

11.5

OTP Programming Warnings

.................................................................................... 52

11.6

OTP Programming Procedure

.................................................................................. 52

12

Always-On (AON) Domain

............................................................................ 53

12.1

AON Power Source

................................................................................................. 54

12.2

AON Clocking

......................................................................................................... 54

12.3

AON Reset Unit

...................................................................................................... 54

12.4

External Reset Circuit

.............................................................................................. 54

12.5

Reset Cause

........................................................................................................... 55

12.6

Watchdog Timer (WDT)

........................................................................................... 55

12.7

Real-Time Clock (RTC)

............................................................................................ 55

12.8

Backup Registers

.................................................................................................... 55

12.9

Power-Management Unit (PMU)

............................................................................... 55

12.10

AON Memory Map

................................................................................................. 55

SiFive FE310-G000 Manual: v3p2

© SiFive, Inc.

Page 3

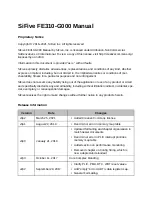

Содержание FE310-G000

Страница 1: ...SiFive FE310 G000 Manual v3p2 SiFive Inc ...