16.1

GPIO Instance in FE310-G000

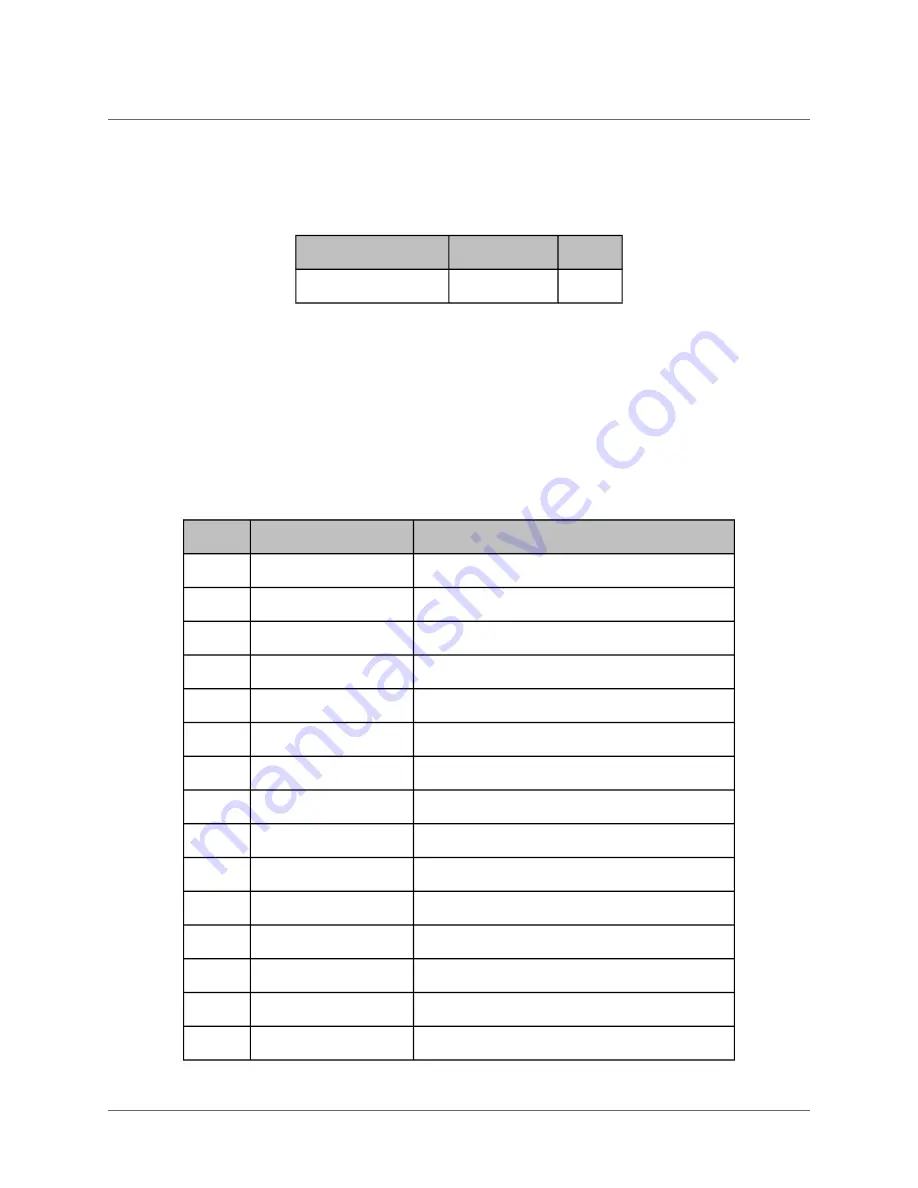

FE310-G000 contains one GPIO instance. Its address and parameters are shown in Table 46.

Table 46:

GPIO Instance

Instance Number

Address

ngpio

0

0x10012000

32

16.2

Memory Map

The memory map for the GPIO control registers is shown in Table 47. The GPIO memory map

has been designed to require only naturally-aligned 32-bit memory accesses. Each register is

ngpio

bits wide.

Offset

Name

Description

0x00

input_val

Pin value

0x04

input_en

Pin input enable*

0x08

output_en

Pin output enable*

0x0C

output_val

Output value

0x10

pue

Internal pull-up enable*

0x14

ds

Pin drive strength

0x18

rise_ie

Rise interrupt enable

0x1C

rise_ip

Rise interrupt pending

0x20

fall_ie

Fall interrupt enable

0x24

fall_ip

Fall interrupt pending

0x28

high_ie

High interrupt enable

0x2C

high_ip

High interrupt pending

0x30

low_ie

Low interrupt enable

0x34

low_ip

Low interrupt pending

0x38

iof_en

I/O function enable

Table 47:

GPIO Peripheral Register Offsets. Only naturally aligned 32-bit memory accesses

are supported. Registers marked with an * are asynchronously reset to 0. All other registers are

synchronously reset to 0.

Chapter 16 General Purpose Input/Output Controller

SiFive FE310-G000 Manual: v3p2

© SiFive, Inc.

Page 73

Содержание FE310-G000

Страница 1: ...SiFive FE310 G000 Manual v3p2 SiFive Inc ...