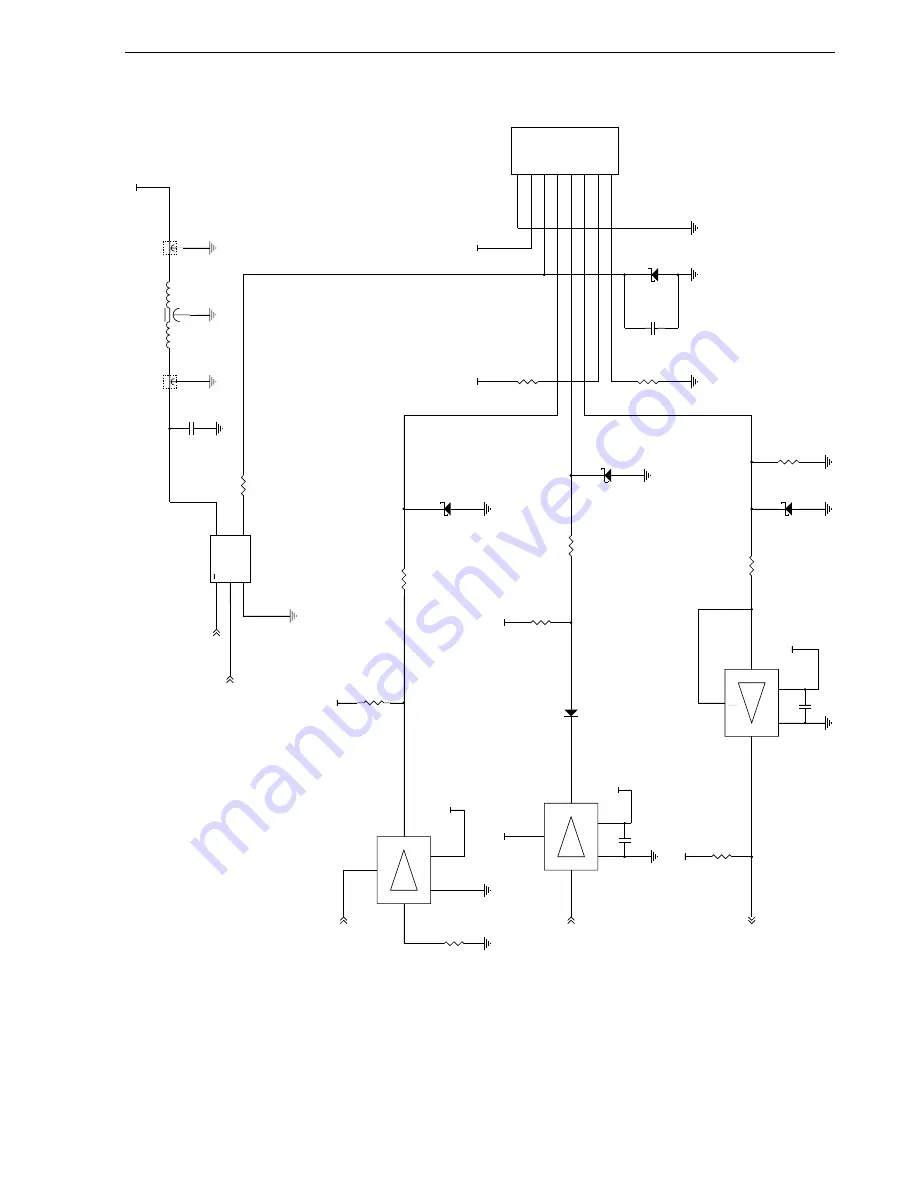

CHAPTER 8 CIRCUIT DIAGRAMS

User’s Manual U17454EJ1V0UM

71

Figure 8-2. Target Interface Block

VDD

VDD

VCC_USB

VCC_USB

VDD

VCC_USB

VCC_USB

VDD

VCC_USB

VDD

RTS_Z

2

FTDI_TXD

2

FTDI_RXD

2

RTS_Z

2

CLK

1

not mount

*

* CLOCK LINE

R16

27

Ω

D6

VDZ6.8B

1

2

D3

VDZ6.8B

1

2

U9

SN74AHCT1G125DCK

GND

3

OE

1

VC C

5

A

4

Y

2

C22

10000pF

R21

27

Ω

E5

NFM18PC104R1C3

1

2

3

R15 4.7 K

Ω

U8B

SN74AHC2G126DCK

GND

4

OE

7

VC C

8

A

5

Y

3

R20

27

Ω

D4

CRS01

U7

TC7SZ125FU

VCC

5

G

1

OUT Y

4

IN A

2

GND

3

D5

VDZ6.8B

1

2

E4

NFM60R30T222

1

2

3

R17 4.7 K

Ω

C21

0.1uF

R18

27

Ω

C19

0.1uF

U8A

SN74AHC2G126DCK

GND

4

OE

1

VC C

8

A

2

Y

6

R19 4.7 K

Ω

D7

VDZ6.8B

1

2

E6

NFM18PC104R1C3

1

2

3

CN2

DF3A-8P-2DSA

GND

1

VDD

2

CLK

3

/RESET

4

TXD

5

RXD

6

FLMD0

7

FLMD1

8

R23

27

Ω

R24 100K

Ω

C20

10000pF

R22 4.7 K

Ω

R14

120

Ω

*

Содержание PG-FPL3

Страница 2: ...User s Manual U17454EJ1V0UM 2 MEMO ...