Rev. 3.0, 10/02, page 307 of 686

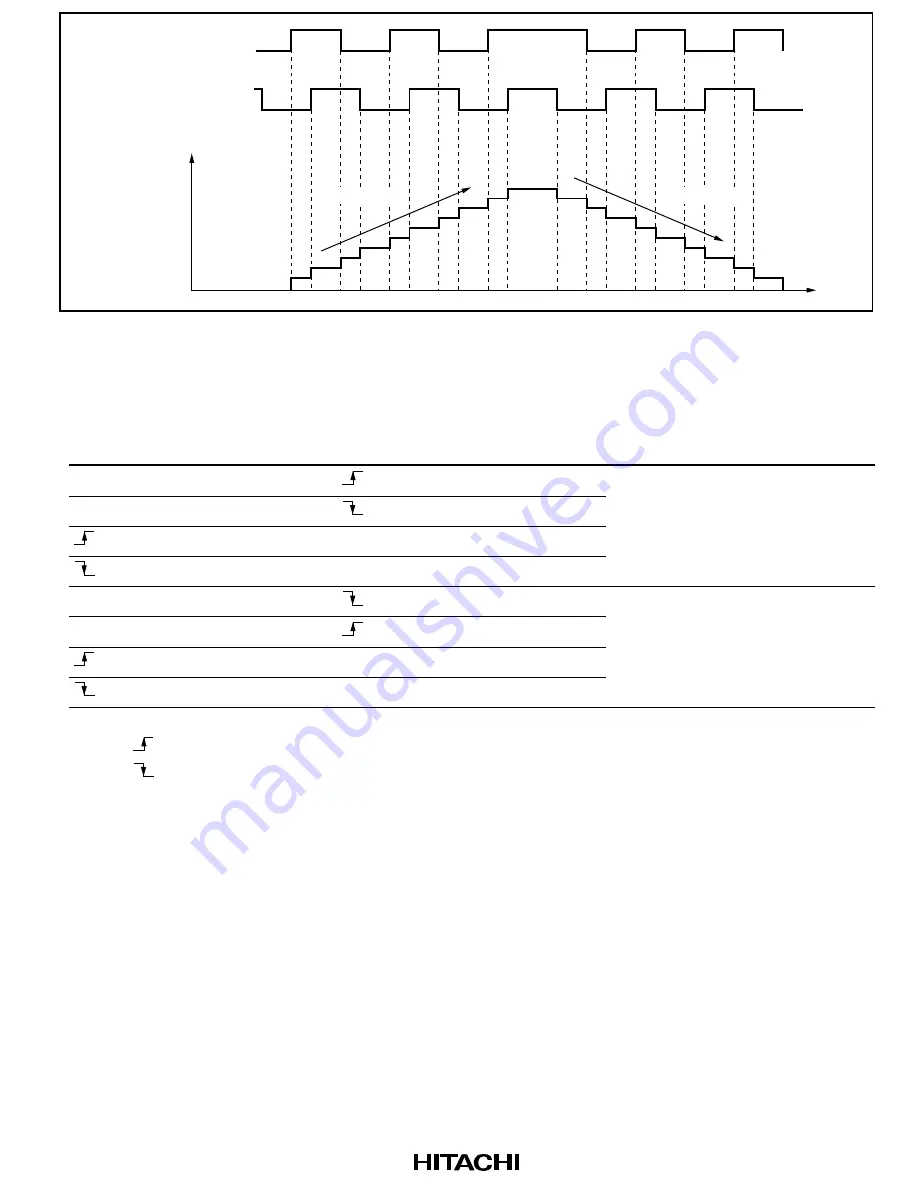

TCNT value

Time

Down-count

Up-count

TCLKA (channel 1)

TCLKC (channel 2)

TCLKB (channel 1)

TCLKD (channel 2)

Figure 10.26 Example of Phase Counting Mode 1 Operation

Table 10.20 Up/Down-Count Conditions in Phase Counting Mode 1

TCLKA (Channel 1)

TCLKC (Channel 2)

TCLKB (Channel 1)

TCLKD (Channel 2)

Operation

High level

Low level

Low level

High level

Up-count

High level

Low level

High level

Low level

Down-count

Legend:

: Rising edge

: Falling edge

2. Phase counting mode 2

Figure 10.27 shows an example of phase counting mode 2 operation, and table 10.21

summarizes the TCNT up/down-count conditions.

Содержание H8S/2215 Series

Страница 4: ...Rev 3 0 10 02 page iv of lviii ...

Страница 6: ...Rev 3 0 10 02 page vi of lviii ...

Страница 28: ...Rev 3 0 10 02 page xxviii of lviii ...

Страница 122: ...Rev 3 0 10 02 page 64 of 686 ...

Страница 132: ...Rev 3 0 10 02 page 74 of 686 ...

Страница 156: ...Rev 3 0 10 02 page 98 of 686 ...

Страница 198: ...Rev 3 0 10 02 page 140 of 686 ...

Страница 320: ...Rev 3 0 10 02 page 262 of 686 ...

Страница 384: ...Rev 3 0 10 02 page 326 of 686 ...

Страница 474: ...Rev 3 0 10 02 page 416 of 686 ...

Страница 481: ...Rev 3 0 10 02 page 423 of 686 I O pin Control OUT IN TDI pin TDO pin Figure 14 2 Boundary Scan Register Configuration ...

Страница 608: ...Rev 3 0 10 02 page 550 of 686 ...

Страница 614: ...Rev 3 0 10 02 page 556 of 686 ...

Страница 650: ...Rev 3 0 10 02 page 592 of 686 ...

Страница 652: ...Rev 3 0 10 02 page 594 of 686 ...

Страница 680: ...Rev 3 0 10 02 page 622 of 686 ...

Страница 721: ...Rev 3 0 10 02 page 663 of 686 ø A23 to A0 to tBRQS tBACD tBZD tBACD tBZD tBRQS Figure 24 11 External Bus Release Timing ...

Страница 732: ...Rev 3 0 10 02 page 674 of 686 ...

Страница 740: ...Rev 3 0 10 02 page 682 of 686 ...