HDMI 1.4/2.0 TX Subsystem

27

PG235 October 4, 2017

Chapter

2:

Product Specification

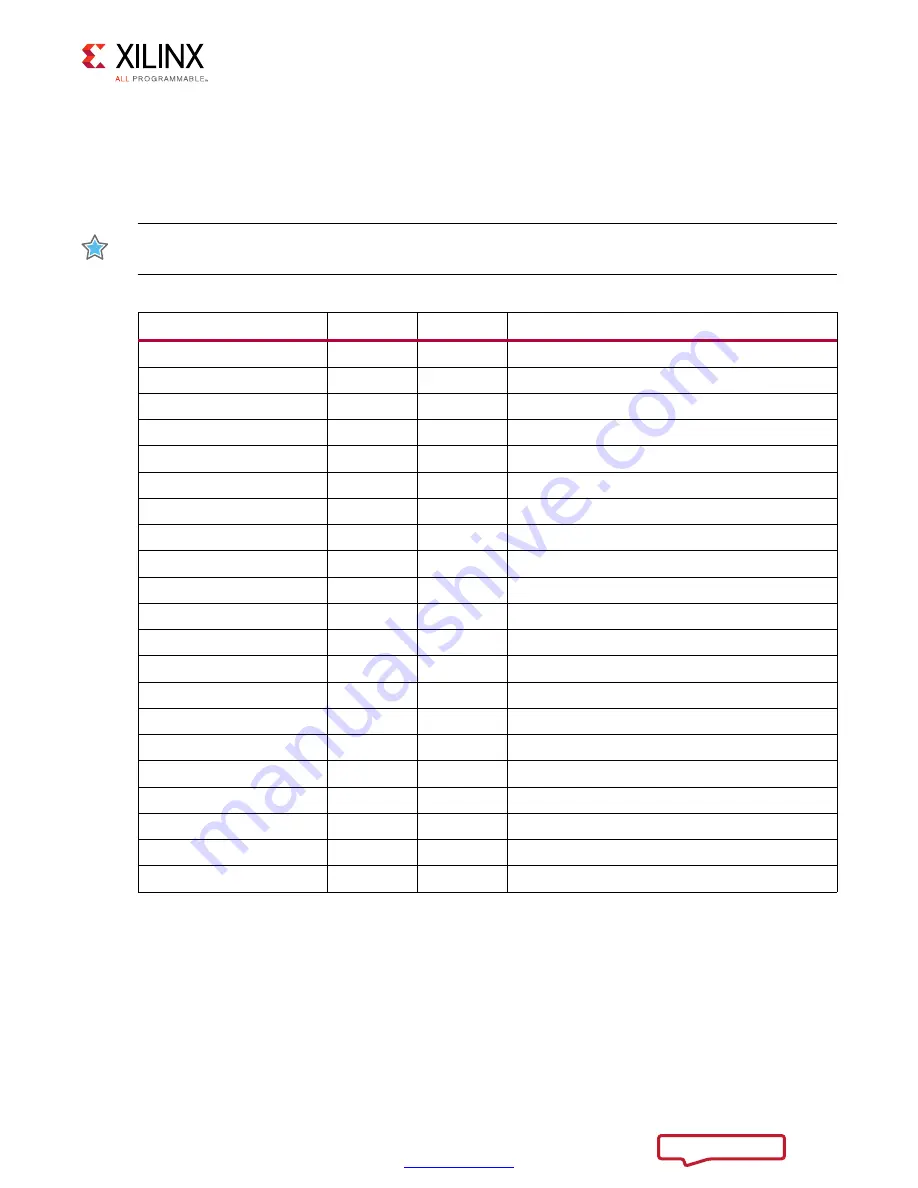

CPU Interface

shows the AXI4-Lite control interface signals. This interface is an AXI4-Lite

interface and runs at the

s_axi_cpu_aclk

clock rate. Control of the subsystem is only

supported through the subsystem driver.

IMPORTANT:

The direct register level access to any of the submodules is not supported. Instead, all the

accesses are done through driver APIs.

Table

2

‐

1:

CPU Interface Ports

Name

Direction

Width

Description

s_axi_cpu_aresetn

Input 1

Reset

(Active-Low)

s_axi_cpu_aclk

Input 1

Clock

for AXI4-Lite control interface

S_AXI_CPU_IN_awaddr

Input 17

Write

address

S_AXI_CPU_IN_awprot Input 3

Write address protection

S_AXI_CPU_IN_awvalid

Input

1

Write address valid

S_AXI_CPU_IN_awready

Output

1

Write address ready

S_AXI_CPU_IN_wdata

Input 32

Write

data

S_AXI_CPU_IN_wstrb

Input 4

Write

data

strobe

S_AXI_CPU_IN_wvalid

Input 1

Write

data

valid

S_AXI_CPU_IN_wready

Output

1

Write data ready

S_AXI_CPU_IN_bresp

Output

2

Write response

S_AXI_CPU_IN_bvalid

Output

1

Write response valid

S_AXI_CPU_IN_bready

Input

1

Write response ready

S_AXI_CPU_IN_araddr

Input 17

Read

address

S_AXI_CPU_IN_arprot

Input

3

Read address protection

S_AXI_CPU_IN_arvalid

Input

1

Read address valid

S_AXI_CPU_IN_aready

Output

1

Read address ready

S_AXI_CPU_IN_rdata

Output

32

Read data

S_AXI_CPU_IN_rresp

Output

2

Read data response

S_AXI_CPU_IN_rvalid

Output

1

Read data valid

S_AXI_CPU_IN_rready

Input

1

Read data ready