HDMI 1.4/2.0 TX Subsystem

57

PG235 October 4, 2017

Chapter

4:

Design Flow Steps

Constraining the Subsystem

This section contains information about constraining the subsystem in the Vivado Design

Suite.

Required Constraints

There are clock frequency constraints for the

s_axi_cpu_aclk

,

s_axis_video_aclk

,

s_axis_audio_aclk

,

link_clk

, and

video_clk

. For example,

create_clock -name s_axi_cpu_aclk -period 10.0 [get_ports s_axi_cpu_aclk]

create_clock -name s_axis_audio_aclk -period 10.0 [get_ports s_axis_audio_aclk]

create_clock -name link_clk -period 13.468 [get_ports link_clk]

create_clock -name video_clk -period 6.734 [get_ports video_clk]

create_clock -name s_axis_video_aclk -period 5.0 [get_ports s_axis_video_aclk]

When using this subsystem in the Vivado® Design Suite flow with Video PHY Controller

modules,

link_clk

and

video_clk

are generated from the Video PHY Controller.

Therefore, the clock constraints are set to the Video PHY Controller constraints instead of

these generated clocks. See

Clocking

in the

Video PHY Controller LogiCORE™ IP Product

Guide

(PG230)

s_axi_cpu_aclk

,

s_axis_video_aclk

, and

s_axis_audio_aclk

constraints are

generated at system-level, for example by using a clock wizard.

Device, Package, and Speed Grade Selections

For more information on the device constraint/dependency, see the

Video PHY Controller

LogiCORE IP Product Guide

(PG230)

.

shows the device and speed grade selections for HDMI 1.4/2.0 Transmitter

Subsystem.

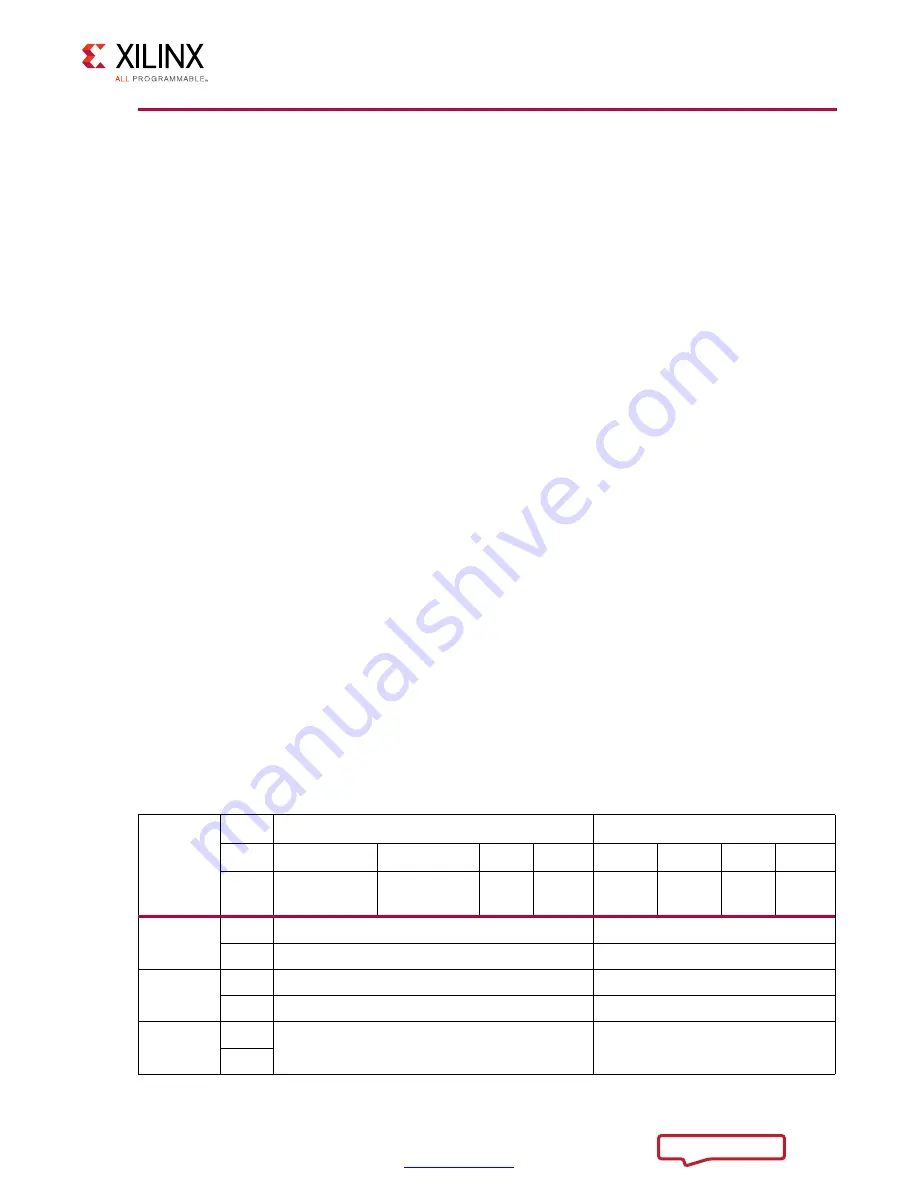

Table

4

‐

2:

Device and Speed Grade Selections

Device

Family

PPC

2

4

BPC

8

10

12

16

8

10

12

16

Speed

Grade

Artix-7

–1

HDMI 1.4

HDMI 1.4

–2

HDMI 1.4

HDMI 1.4

Kintex-7

–1

HDMI 1.4

HDMI 1.4

–2

HDMI 2.0

HDMI 2.0

Kintex

UltraScale

–1

HDMI 2.0

HDMI 2.0

–2