HDMI 1.4/2.0 TX Subsystem

7

PG235 October 4, 2017

Chapter 2

Product Specification

This chapter includes a description of the subsystem and details about the performance and

resource utilization.

Introduction

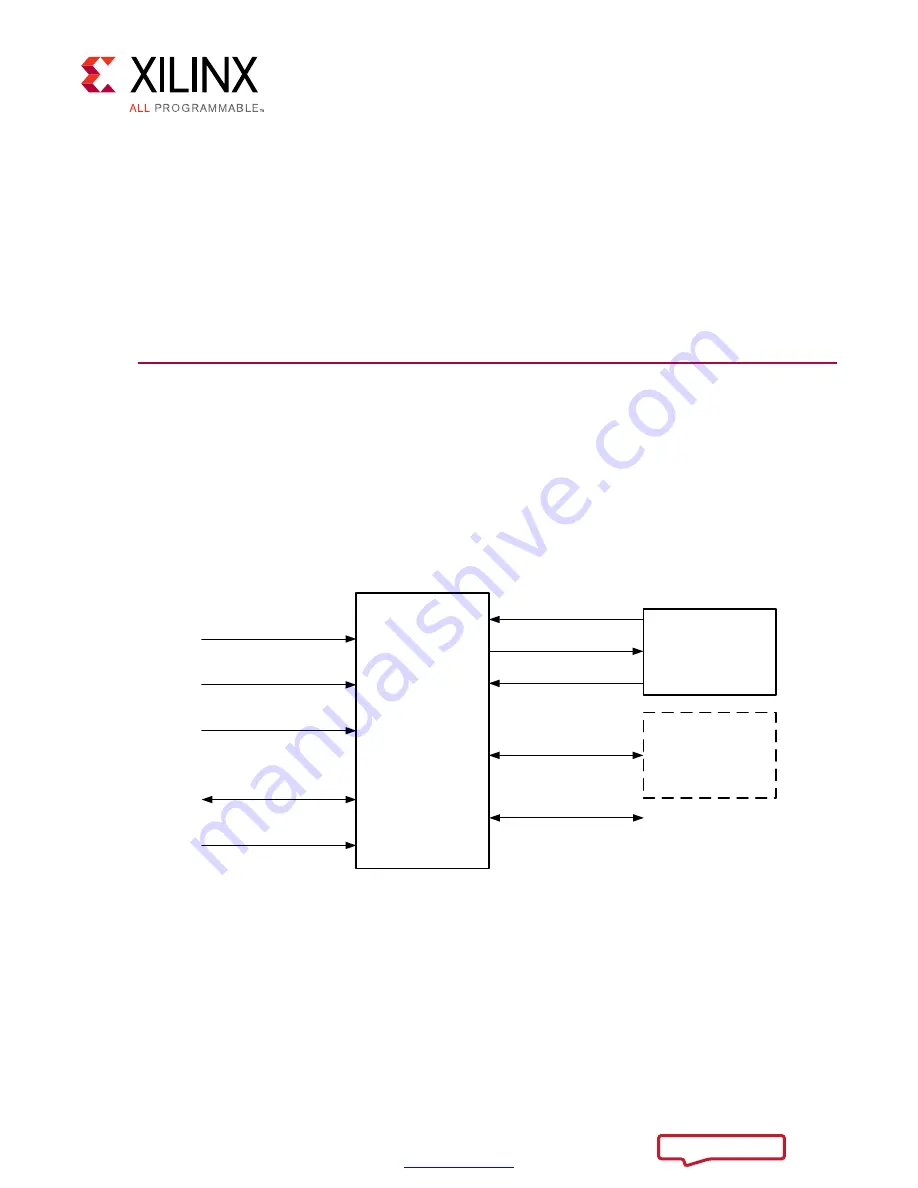

Because the HDMI 1.4/2.0 Transmitter Subsystem is hierarchically packaged, you can

configure it by setting the parameters in the Vivado® Integrated Design Environment (IDE)

interface and the subsystem creates the required hardware accordingly.

A high-level block diagram of the HDMI 1.4/2.0 Transmitter Subsystem is shown in

.

The HDMI TX Subsystem is constructed on top of an HDMI TX core. Various supporting

modules are added around the HDMI TX core with respect to your configuration. The HDMI

TX core is designed to support native video interface, however many of the existing video

processing IP cores are AXI4-Stream based. It is a natural choice to add some supporting

modules (Video Timing Controller and AXI4-Stream to Video Out Bridge) to construct

HDMI TX Subsystem to be able to supportAXI4-Stream based video. By performing this,

HDMI TX Subsystem is able to work seamlessly with other Xilinx video processing IP cores.

X-Ref Target - Figure 2-1

Figure

2

‐

1:

Subsystem Block Diagram

+'0,7;

6XEV\VWHP

&38,QWHUIDFH

$;,/LWH

9LGHR,QWHUIDFH

$XGLR,QWHUIDFH

$;,6WUHDP

$;,6WUHDP1DWLYH9LGHR

''&

+3'

3+<

/D\HU

/LQN'DWD

/LQN&ORFN

0LVFHOODQHRXV

9LGHR&ORFN

+'&3.H\

0DQDJHPHQW

+'&3.H\

;