2-9

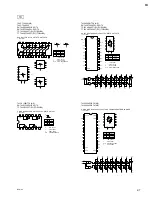

BVW-55

IC

1

2

3

4

5

6

7

8

9

10

11

12

VA

A GND

VD

AINR

+

IN

AINR

_

IN

VREF

OUT

AINL

+

IN

AINL

_

IN

TST1

HPFE

IN

TST2

TST3

24

23

22

21

20

19

18

17

16

15

14

13

6

7

1

2

22

17

23

15

9

16

8

10

11

14

SDATA

SCLK

L/R

FSYNC

VREF

21

18

19

20

3

AINL

+

AINL

_

AINR

+

AINR

_

CMODE

MCLK

SMODE1

SMODE2

HPFE

PD

TST1

TST2

TST3

TST4

VB

D GND

SMODE1

IN

CMODE

IN

SDATA

OUT

FSYNC

I/O

L/

R

I/O

SCLK

I/O

MCLK

IN

PD

IN

SMODE2

IN

TST4

C-MOS 20-BIT A/D CONVERTER

—TOP VIEW—

: CHANNEL L ANALOG POSITIVE INPUT

: CHANNEL L ANALOG NEGATIVE INPUT

: CHANNEL R ANALOG POSITIVE INPUT

: CHANNEL R ANALOG NEGATIVE INPUT

: MASTER CLOCK SELECT

(L : MCLK = 256 fs)

(H : MCLK = 384 fs)

: HIGH PASS FILTER ENABLE

(L : OFF)

(H : ON)

: MASTER CLOCK

(CMODE = H : 384 fs)

(CMODE = L : 256 fs)

: POWER DOWN

(L : POWER DOWN MODE)

: INTERFACE CLOCK SELECT

: SERIAL DATA

: REFERENCE VOLTAGE

: FRAME SYNC CLOCK

: INPUT CHANNEL SELECT

(SUB MODE : fs CLK INPUT)

(MASTER MODE : fs CLK OUTPUT)

: SERIAL DATA CLOCK

(SUB MODE : 64 fs CLK INPUT)

(MASTER MODE : 64 fs CLK OUTPUT)

MODE

SUB MODE

MASTER MODE

SUB MODE

MASTER MODE

SMODE2

L

L

H

H

SMODE1

L

H

L

H

LRCK

H/L

H/L

L/H

L/H

INPUT

AINL

+

AINL

_

AINR

+

AINR

_

CMODE

HPFE

MCLK

PD

SMODE1, SMODE2

OUTPUT

SDATA

VREF

INPUT/OUTPUT

FSYNC

L/

R

SCLK

6

AINL

+

DIGITAL

DECIMATION

FILTER

T

∑

MODULATOR

7

AINL

_

1

AINR

+

T

∑

MODULATOR

2

AINR

_

VOLTAGE

REFERENCE

3

VREF

22

CMODE

CLOCK

DIVIDER

17

MCLK

SERIAL

OUTPUT

INTERFACE

16

PD

9

HPFE

POWER DOWN

HIGH PASS FILTER ENABLE

21

SDATA

18

SCLK

19

L/

R

20

FSYNC

15

SMODE2

23

SMODE1

AK5352-VF-E2 (ASAHI)

1

2

3

4

RDY/

BUSY

CS

SK

DI

DO

RDY/

BUSY

6

1

8

16

16

CS

SK

RESET

5

3

4

8

GND

8

7

6

5

RESET

DO

DI

INPUT

CS

DI

RESET

SK

OUTPUT

DO

RDY/

BUSY

: CHIP SELECT

: DATA INPUT

: RESET

: SERIAL CLOCK

: DATA OUTPUT

: READY/BUSY

DATA

REGISTER

ADD

BUFFERS

INSTRUCTION

DECODER

CONTROL

AND

CLOCK

GENERATION

INSTRUCTION

REGISTER

R/W

AMPS

AND

AUTO

ERASE

DECODER

VPP SW

V REF

EE

PROM

2048-BIT

(128

x

16)

VPP

GENERATOR

V

DD

14

7

14

C-MOS 2,048 (128

x

16)-BIT EEPROM

—TOP VIEW—

AK6420AF-E2 (ASAHI)

1

2

3

4

5

6

7

8

16

15

14

13

EN2

12

11

10

9

GND

V

CC

FUNCTION TABLE

EN2

0

0

1

1

EN1

0

1

0

1

OUTPUT

ENABLE

ENABLE

HI-Z

ENABLE

C32/LS32

LS33

SENSE

±

200mV

±

500mV

INPUT VOLT

±

7 V

±

15 V

_ +

_

+

+_

_+

HIGH SPEED DIFFERENTIAL LINE RECEIVER

—TOP VIEW—

0

1

HI-Z

: LOW LEVEL

: HIGH LEVEL

: HIGH IMPEDANCE

AM26LS32ACNS (TI)

AM26LS32ACNS-E05

Summary of Contents for BVW-55

Page 4: ......

Page 8: ......

Page 50: ...1 40 BVW 55 1 2 3 4 5 6 7 8 9 d l s d l 1 15 Fixtures and Adjustment Equipment List ...

Page 58: ......

Page 106: ......

Page 116: ......

Page 130: ......

Page 148: ......

Page 154: ......

Page 158: ......

Page 169: ...1 9 BVW 55 P2 1 2 Fixtures and Adjustment Equipment List 1 2 3 4 5 6 7 8 9 d l s d l ...

Page 176: ......

Page 272: ......

Page 384: ......

Page 392: ......

Page 396: ...1 2 BVW 55 ...

Page 666: ......

Page 705: ......

Page 752: ......

Page 780: ......

Page 805: ......

Page 848: ......

Page 856: ......

Page 870: ......

Page 884: ......

Page 904: ......

Page 909: ...5 27 b BVW 55 5 27 b CN101 CN301 CN302 CN303 CN901 MB 838 B SIDE SUFFIX 12 MB 838 MB 838 ...

Page 911: ...5 27 a BVW 55 5 27 a CN101 CN301 CN302 CN303 CN901 MB 838 B SIDE SUFFIX 11 MB 838 MB 838 ...

Page 940: ......