UP-5900VS

BIOS SETUP UTILITY

6 – 1

CHAPTER 6. BIOS SETUP UTILITY

1. OUTLINE

In UP-5900, there is a utility that rewrites minimum required setup infor-

mation at the system boot up that resides in ROM-BIOS.

Setup data is undefined at the first system startup, so setup must be

done. Basically, just doing initial setting in setup can do system opera-

tion.

Also, BIOS in UP-5900 will automatically detects memory size / HDD,

which makes no need for running setup again after changing hardware

(expanding memory, changing HDD, etc).

However, adding / removing second HDD will require running menu for-

mat setup.

2. STARTING PROCEDURE

There are 2 ways of starting setup, changing system SW and connect-

ing PS/2 type full keyboard. Setup started by each procedure will be as

follows.

2-1. STARTING SETUP BY CHANGING SYSTEM SW

Setup data initialization will be processed when system is started with

system SW (JP2) turned on.

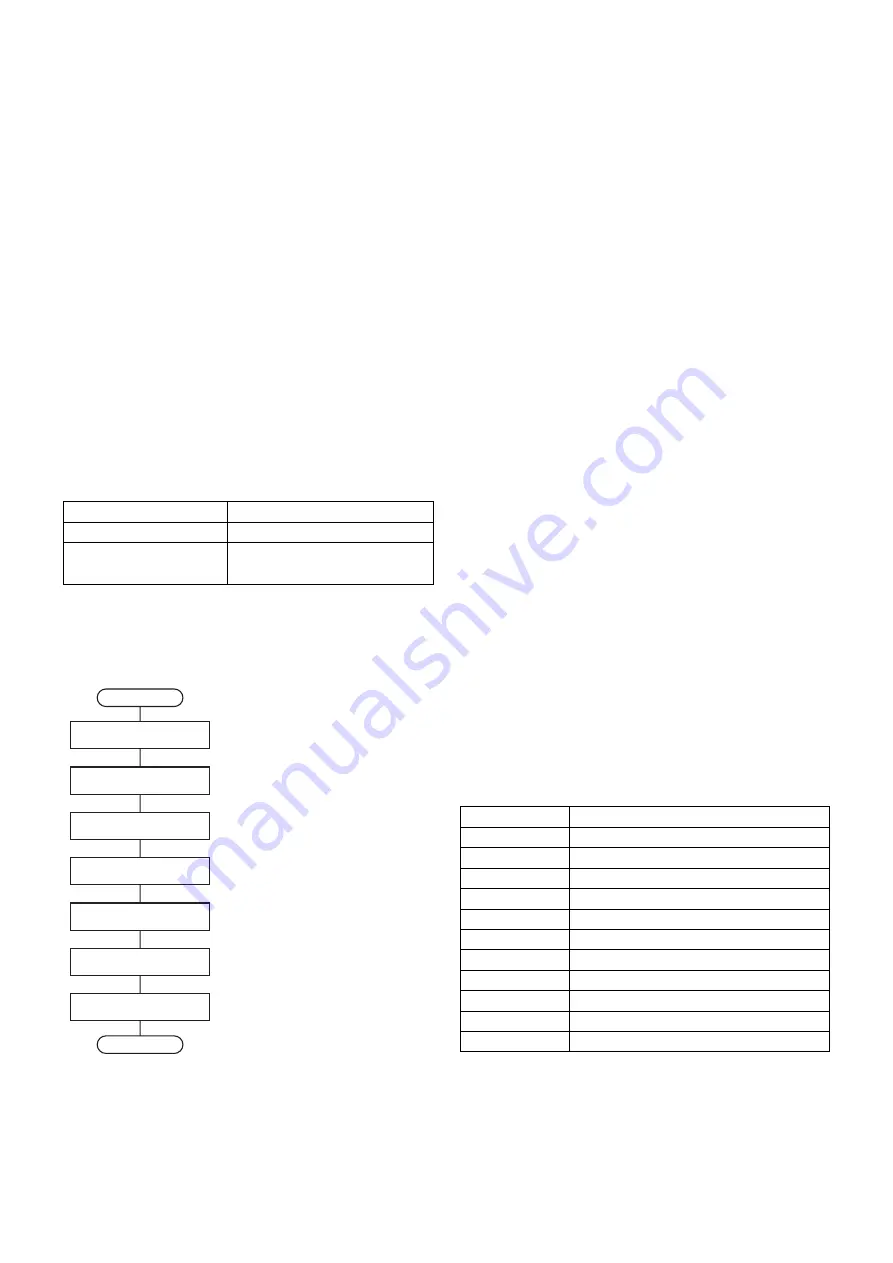

Following shows the flow of this procedure.

2-2. STARTING SETUP WITH FULL KEYBOARD

Starting and operating setup with full keyboard will require UP-C30PK,

PS/2 type full keyboard.

In this setup will use only numpad.

Procedure for starting setup is as follows.

(1) Start the system.

(2) On numpad, press period key when as following message appears

on screen.

“SETUP Available”

(3) If bios accepts above key, as following message appears on

screen.

“Entering SETUP...”

(4) Press following keys according to setup wanted while “Waiting

SETUP Entry Key ...” message appears on screen.

• Do setup initialization

3

On numpad, press 8 and period at continuously.

Buzzer beeps 3 times and “CMOS Initialize Complete - Please

Restart.” message appears on screen. After this message, turn

off system power

• Starting setup in menu format

3

On numpad, press 7 and period at continuously.

After 1 beep, menu will be displayed.

3. SETUP OUTLINE IN MENU FORMAT

Setup in menu format is not required during normal operation. Use only

in case such as checking contents of setup during maintenance, or

modifying setup contents required due to system operation.

3-1. KEY ASSIGNMENTS

Following num keys are used during operation of setup in menu format.

Setup in the menu format displays key assignment described in the

lower 2 lines. There is a case where [Continue] and [OK] are displayed

during help and in some settings. In this case, press arbitrary key to go

to next step.

Press period when [Press Enter] is displayed.

Procedure for running setup

Setup contents

Start with system SW

• Setup data initialization.

Start with full keyboard

• Setup data initialization.

• Running setup in menu format.

Start

Turn off system power

Change system SW (JP2)

to on position

Turn on system power

Buzzer beeps 3 times

Message displays notifying

initialization complete

Turn off system power

End

Change system SW (JP2)

to off position

; Always turn off power when

changing system SW

; "CMOS Initialize Complete - Please Restart."

; Setup data initialization complete

Key used

Functions

5

Display help

3 (Pg Dn)

Change setting (reverse)

9 (Pg Up)

Change setting (forward)

7 (Home)

Initialize all category displayed

1 (End)

Return to previous value

8 (

2

)

Change category (up)

2 (

4

)

Change category (down)

4 (

1

)

Change menu (left)

6 (

3

)

Change menu (right)

. (Del)

Select submenu, confirm, execute

0 (Ins)

End, return from submenu