Technical Information 1-25

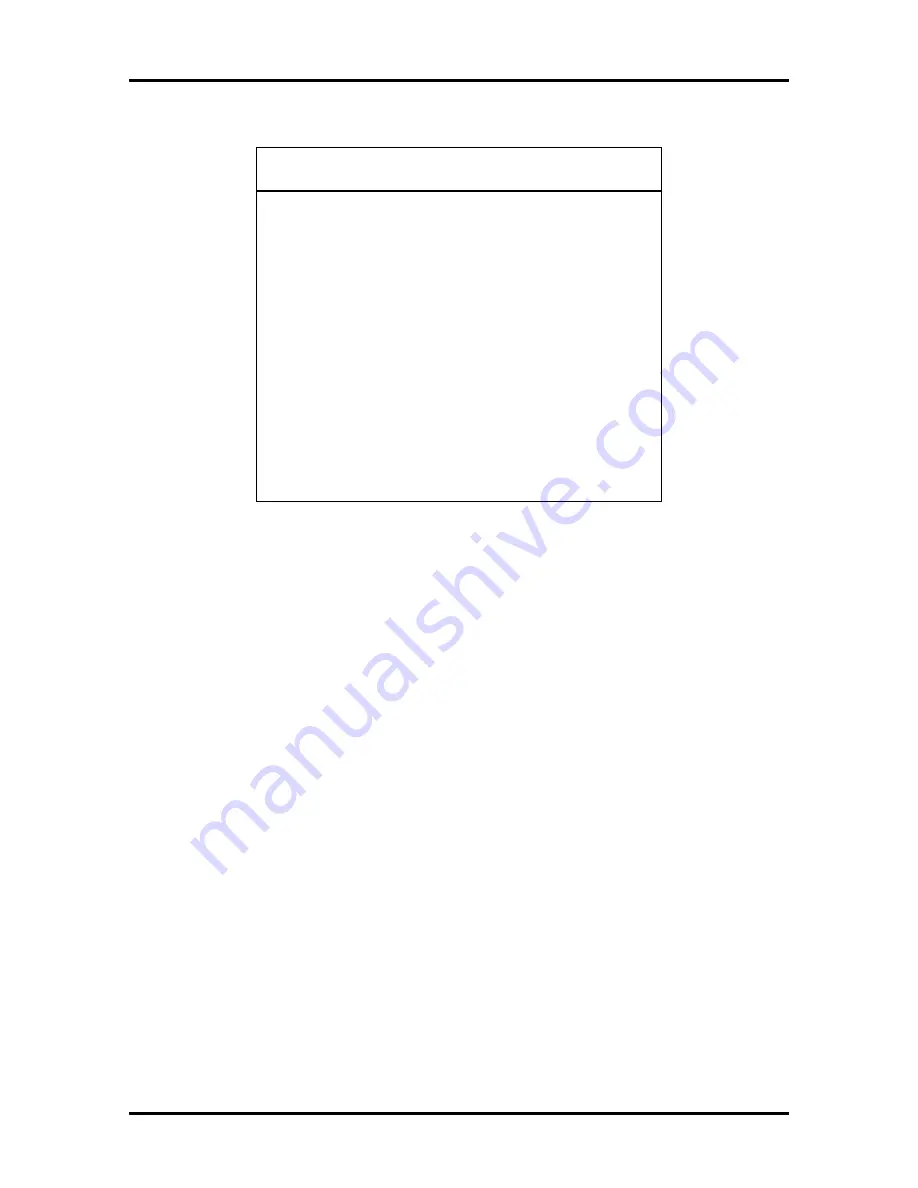

Table Section 1-6 DMA Cycles and Compatible DMA Devices

DMA Cycle

Transfer

Rate (MB/s)

Compatible

DMA Devices

Compatible

8-bit

16-bit

1.0

2.0

All ISA

All ISA

Type A

8-bit

16-bit

32-bit

1.3

2.6

5.3

Most ISA

Most ISA

EISA only

Type B

8-bit

16-bit

32-bit

2.0

4.0

8.0

Some ISA

Some ISA

EISA only

Burst DMA (Type C)

8-bit

16-bit

32-bit

8.2

16.5

33.0

EISA only

EISA only

EISA only

EISA’s bus master archictecture supports intelligent peripherals. The bus master

architecture provides a high-speed data channel with data rates up to 33 MB per second

using EISA Burst cycles. The bus master provides local intelligence by including a

dedicated I/O processor and local memory. It can relieve the burden on the processor by

performing sophisticated memory access functions, such as non-ordered, scatter-gather

data transfers.

The EISA bus provides a way for EISA expansion boards and ISA-compatible devices to

communicate. EISA data and control signals are generated by the bus master or slave. This

lets the system board copy the data to the appropriate byte lanes and translate the control

signals. Automatic translation is provided by the system board for DMA devices and 16-

and 32-bit EISA devices.

EISA’s centralized arbitration scheme allows efficient bus sharing among multiple EISA

bus masters and DMA devices. The centralized arbitration supports preemption of an

active bus master or DMA device and can reset a device that does not release the bus after

preemption. The bus is granted to DMA devices, DRAM refresh, bus masters, and

processor functions on a rotational basis. This rotation provides a short latency for DMA

devices to assure ISA compatibility and longer latencies for the bus master and processor.

EISA interrupts can be configured for edge- or level-triggered operation. Edge-triggered

operation supplies compatibility with existing, interrupt-driven ISA devices. Level-

triggered operation allows the sharing of a single system interrupt by many EISA devices.