1-38

Computer Group Literature Center Web Site

Programming Issues

1

Receive Interrupt Status Register low

RISRl

89

B

R

Receive Interrupt Status Register high

RISRh

88

B

R

Receive FIFO Output Count

RFOC

30

B

R

Receive Data Register

RDR

F8

B

R

Receive End Of Interrupt Register

REOIR

84

B

W

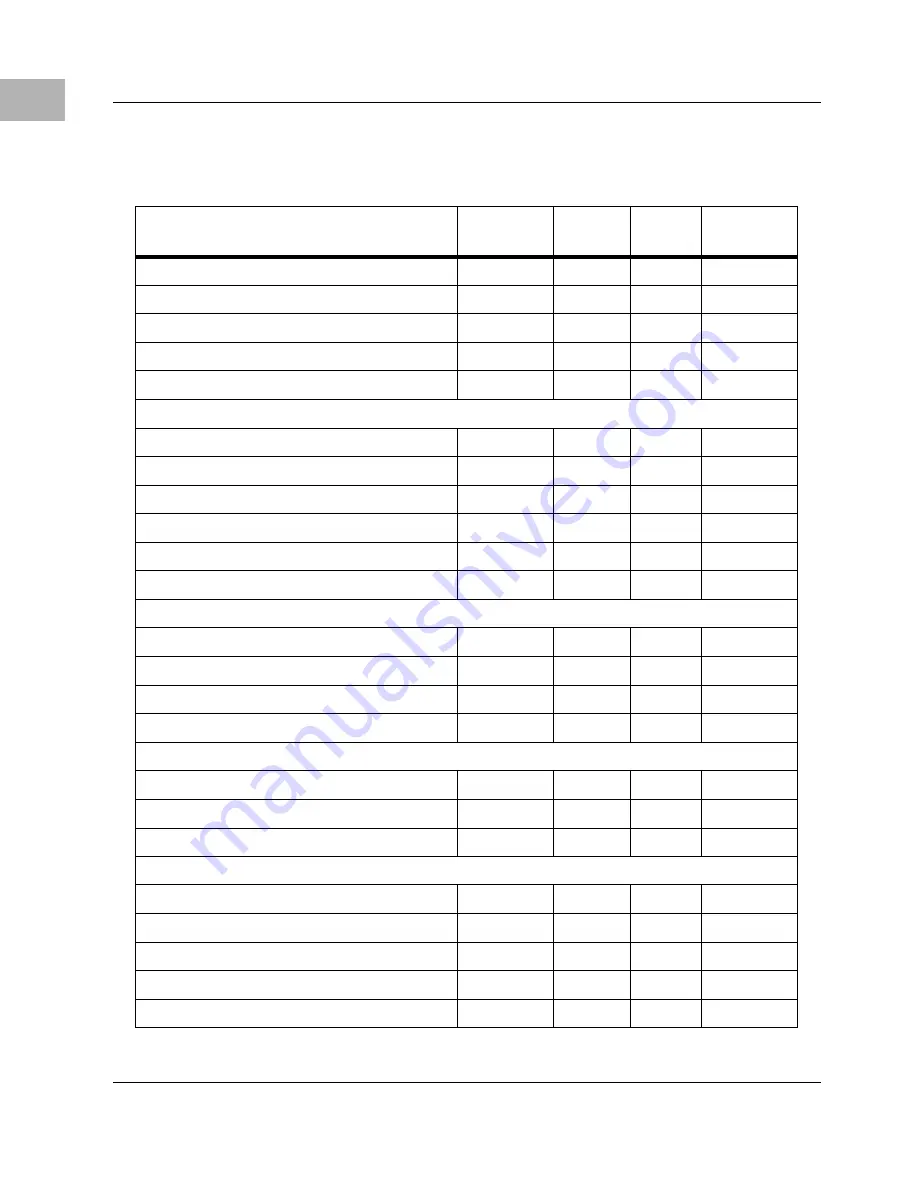

Transmit Interrupt Registers

Transmit Priority Interrupt Level Register

TPILR

E0

B

R/W

Transmit Interrupt Register

TIR

EC

B

R

Transmit Interrupt Status Register

TISR

8A

B

R

Transmit FIFO Transfer Count

TFTC

80

B

R

Transmit Data Register

TDR

F8

B

W

Transmit End Of Interrupt Register

TEOIR

85

B

W

Modem Interrupt Registers

Modem Priority Interrupt Level Register

MPILR

E3

B

R/W

Modem Interrupt Register

MIR

EF

B

R

Modem (/Timer) Interrupt Status Register

MISR

8B

B

R

Modem End Of Interrupt Register

MEOIR

86

B

W

DMA Registers

DMA Mode Register (write only)

DMR

F6

B

W

Bus Error Retry Count

BERCNT

8E

B

R/W

DMA Buffer Status

DMABSTS

19

B

R

DMA Receive Registers

A Receive Buffer Address Lower

ARBADRL

42

W

R/W

A Receive Buffer Address Upper

ARBADRU

40

W

R/W

B Receive Buffer Address Lower

BRBADRL

46

W

R/W

B Receive Buffer Address Upper

BRBADRU

44

W

R/W

A Receive Buffer Byte Count

ARBCNT

4A

W

R/W

Table 1-9. Cirrus Logic CD2401 Serial Port Memory Map (Continued)

Base Address = $FFF45000

Register Description

Register

Name

Offsets

Size

Access

Summary of Contents for MVME1X7P

Page 16: ...xvi ...

Page 18: ...xviii ...

Page 20: ...xx ...

Page 26: ...xxvi ...

Page 90: ...1 64 Computer Group Literature Center Web Site Programming Issues 1 ...

Page 248: ...3 50 Computer Group Literature Center Web Site PCCchip2 3 ...

Page 286: ...4 38 Computer Group Literature Center Web Site MCECC Functions 4 ...

Page 288: ...A 2 Computer Group Literature Center Web Site Summary of Changes A ...

Page 316: ...Index IN 14 Computer Group Literature Center Web Site I N D E X ...