4-14

Computer Group Literature Center Web Site

MCECC Functions

4

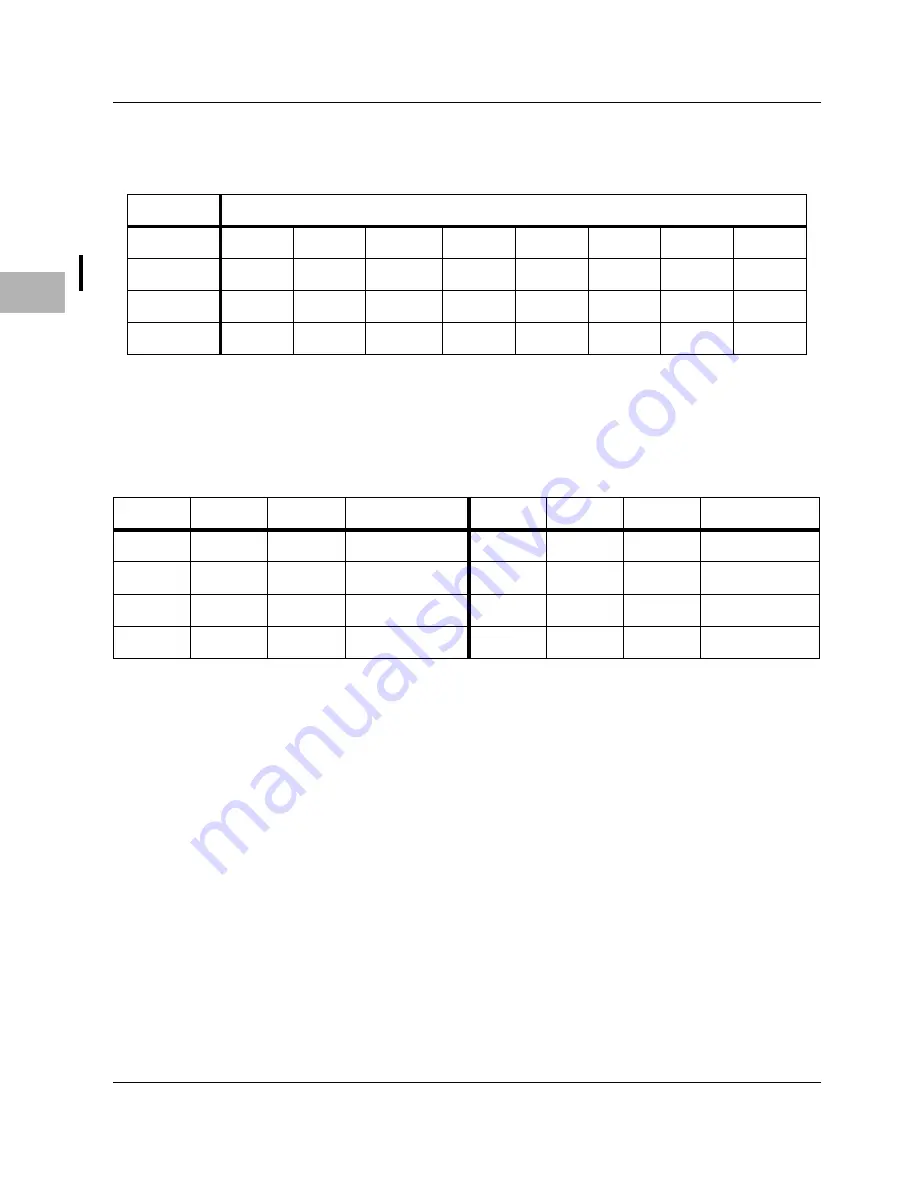

Memory Configuration Register

MSIZ2-MSIZ0

MSIZ2-MSIZ0 together define the size of the total

memory to be controlled by the MCECC sector. These

bits reflect the RSIZ2-RSIZ0 bits in Defaults Register 1.

Note

Remember that the DRAM organization presented in the

table above is relevant to the extent that it aids in emulating

DRAM configurations from earlier programming models.

For the actual SDRAM device and size options now

applicable to the MVME1x7P boards, refer to

Table 1-1

.

FSTRD

FSTRD reflects the state of the FSTRD bit in Defaults

Register 1. When 1, this bit indicates that DRAM reads

are operating at full speed. When 0, it indicates that

DRAM read accesses are slowed by one clock cycle.

ADR/SIZ

1st $FFF43008/2nd $FFF43108 (8-bits)

BIT

31

30

29

28

27

26

25

24

NAME

0

0

FSTRD

0

0

MSIZ2

MSIZ1

MSIZ0

OPER

R

R

R

R

R

R

R

R

RESET

X

X

X

X

X

X

X

X

MSIZ2

MSIZ1

MSIZ0

Memory Size

MSIZ2

MSIZ1

MSIZ0

Memory Size

0

0

0

4MB

1

0

0

64MB

0

0

1

8MB

1

0

1

128MB

0

1

0

16MB

1

1

0

Reserved

0

1

1

32MB

1

1

1

Reserved

Summary of Contents for MVME1X7P

Page 16: ...xvi ...

Page 18: ...xviii ...

Page 20: ...xx ...

Page 26: ...xxvi ...

Page 90: ...1 64 Computer Group Literature Center Web Site Programming Issues 1 ...

Page 248: ...3 50 Computer Group Literature Center Web Site PCCchip2 3 ...

Page 286: ...4 38 Computer Group Literature Center Web Site MCECC Functions 4 ...

Page 288: ...A 2 Computer Group Literature Center Web Site Summary of Changes A ...

Page 316: ...Index IN 14 Computer Group Literature Center Web Site I N D E X ...