LCSR Programming Model

http://www.motorola.com/computer/literature

2-59

2

VMEbus address modifier bits 2-5, and address modifier

bits 0 and 1 are provided by the DMAC to indicate a block

transfer. Block transfer mode should not be set in the

address modifier codes. The special block transfer bits

should be set to enable block transfers. If non-block cycles

are required to reach a 32- or 64-bit boundary, bits 0 and

1 are used during these cycles.

BLK

These bits control the block transfer modes of the DMAC:

0

Block transfers disabled

1

The DMAC executes D32 block transfer cycles

on the VMEbus. In block transfer mode, the

DMAC may execute byte and two-byte cycles

at the beginning and ending of a transfer in

non-block transfer mode. If the D16 bit is set,

the DMAC executes D16 block transfers.

2

Block transfers disabled

3

The DMAC executes D64 block transfer cycles

on the VMEbus. In block transfer mode, the

DMAC may execute byte, two-byte and four-byte

cycles at the beginning and ending of a transfer

in non-block transfer mode. If the D16 bit is set,

the DMAC executes D16 block transfers.

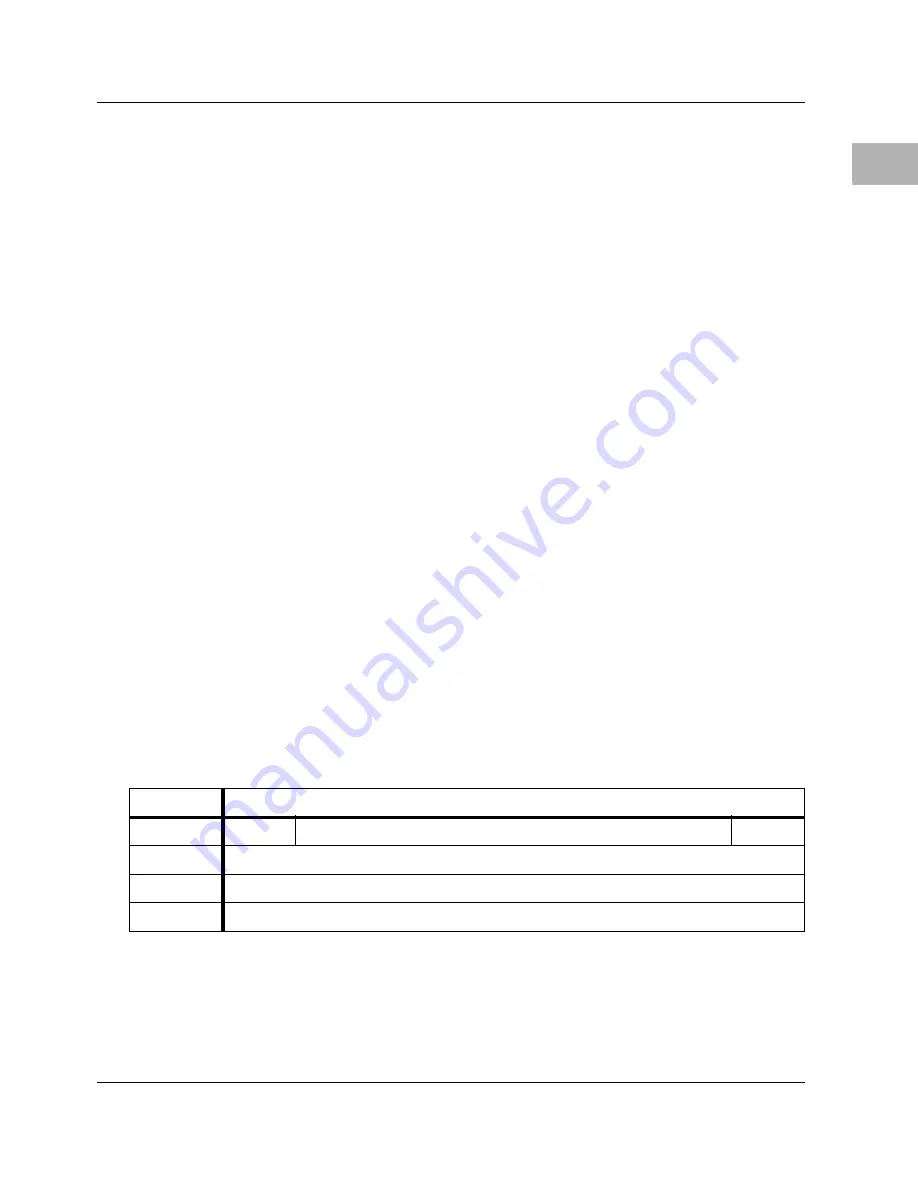

DMAC Local Bus Address Counter

In direct mode, this counter is programmed with the starting address of the

data in local bus memory.

ADR/SIZ

$FFF40038 (32 bits)

BIT

31

. . .

0

NAME

DMAC Local Bus Address Counter

OPER

R/W

RESET

0 PS

Summary of Contents for MVME1X7P

Page 16: ...xvi ...

Page 18: ...xviii ...

Page 20: ...xx ...

Page 26: ...xxvi ...

Page 90: ...1 64 Computer Group Literature Center Web Site Programming Issues 1 ...

Page 248: ...3 50 Computer Group Literature Center Web Site PCCchip2 3 ...

Page 286: ...4 38 Computer Group Literature Center Web Site MCECC Functions 4 ...

Page 288: ...A 2 Computer Group Literature Center Web Site Summary of Changes A ...

Page 316: ...Index IN 14 Computer Group Literature Center Web Site I N D E X ...