IDT sRIO Ports

Revision 1.5

Integrated Device Technology, Inc.

CPS-16/12/8 User Manual

2 - 4

July 10, 2012

The device supports the ability to route a packet which matches the “Trace Criteria” to the port referenced

by the packet’s destination ID (including multicast references) as well as to the trace port.

Each port provides a unique trace circuit such that the user may enable trace on up to 16 simultaneous

ports (4 for each of the 16 ports) as defined below.

2.2.1 Trace Criteria

The property of a given port matching a packet with a “Trace Criteria” refers to a successful comparison of

the first 160 bits in a received packet to multiple pre-programmed values stored at that port. A successful

match against a port’s Trace Criteria triggers a forwarding of the packet to the trace enabled output port.

Each port provides a set of four 160-bit comparison values which can be selectively applied to the first 160

bits of each packet that the port receives. Each port also provide a bit mask for each of the four program-

mable 160 bit comparison values which define which of the first 160 bits of packet data are relevant to the

comparison. A logical value of 1 in the comparison value mask indicate that the corresponding bits in the

programmed value and the corresponding bit in the packet data is compared. A logical value of zero in the

comparison value mask is used as a “don’t care”. A don’t care value results in an automatic match of the

corresponding bits in the programmable value with the corresponding packet data bits. When all bits of the

packet data match with a given corresponding bit in a given programmable value (after the value’s mask

has been applied) the Trace criteria has been met and the packet is forwarded to the trace enabled output

port. The packet trace is triggered by a logical “OR” of the comparison match results (packet data with the

four programmable values) such that if at least one match occurs, packet forwarding to the trace-enabled

port is performed.

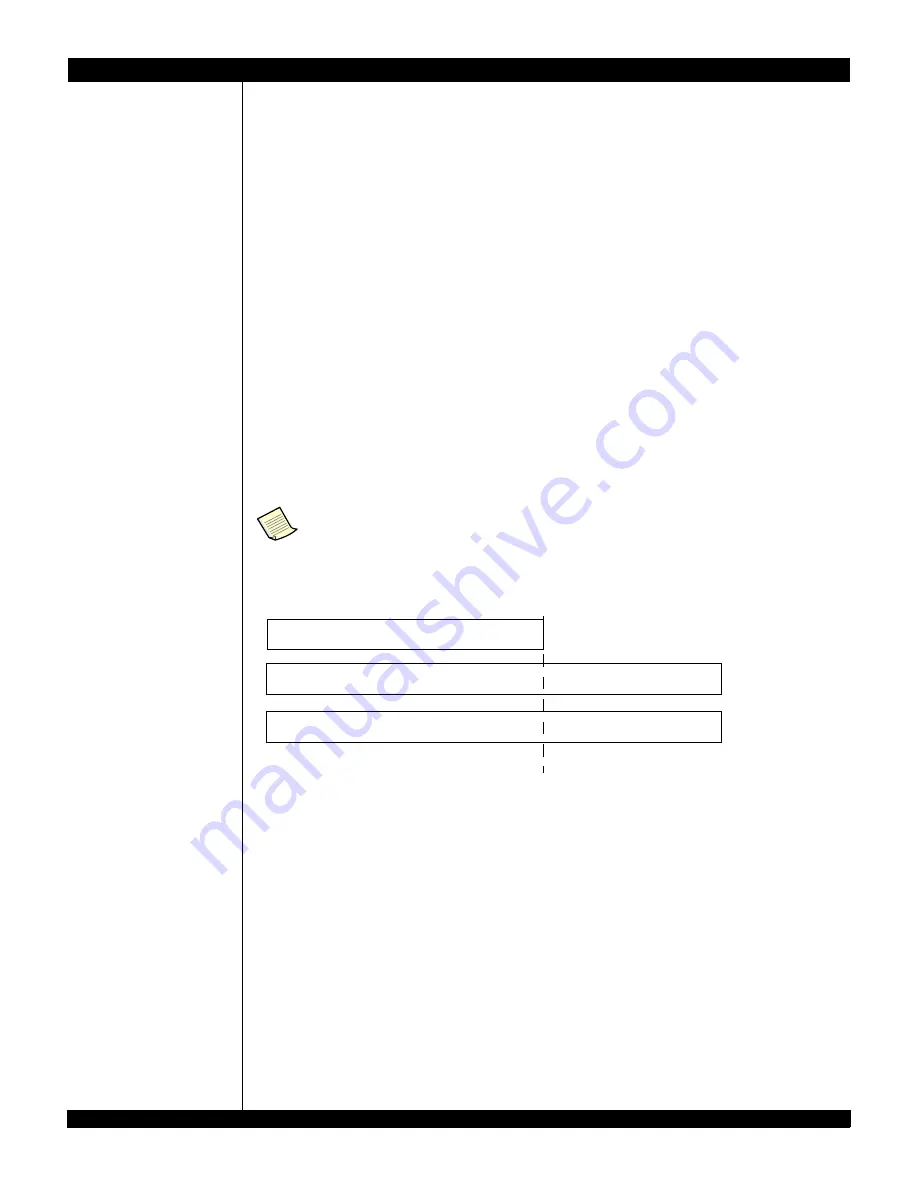

Figure 2.1 Trace Matching Criteria

For clarification, if the user wants to trace a packet which is smaller than 160 bits, the number of mask bits

between the packet size and 160 must be set to don’t care.

A packet which matches any of the four values are forwarded to the trace enabled output port as well as

any other ports referenced by the packet’s destination ID.

The Trace Criteria architecture is illustrated in the diagram below.

The trace criteria is based on the “entire content” of the comparison value and its corresponding

bit mask. This is true in the event that the bit count of the received packet is smaller than 160

bits. In this event, in order to match the trace criteria, the number of bits in the mask which are

greater than the received packet data must be set to don’t cares as shown below.

Packet Data

bit

0

.............................................

.bit

n<160

bit

0

.......................................................................................

.bit

160

Comparison Dat

a

Comparison Mask

bit

0

.............................................

.bit

n<160

X

n+1

................................X

160

X = don’t care