Hitachi 81

•

Bits 15, 7—Reserved bits: These bits always read 0. The write value should always be 0.

•

Bits 14 to 8—Serial communication interface (SCI) transmit-data-empty interrupt vector

number (STXV6–STXV0): These bits set the vector number for the serial communication

interface (SCI) transmit-data-empty interrupt (TXI). There are seven bits, so the value can be

set between 0 and 127.

•

Bits 6 to 0—Serial communication interface (SCI) transmit-end interrupt vector number

(STEV6–STEV0): These bits set the vector number for the serial communication interface

(SCI) transmit-end interrupt (TEI). There are seven bits, so the value can be set between 0 and

127.

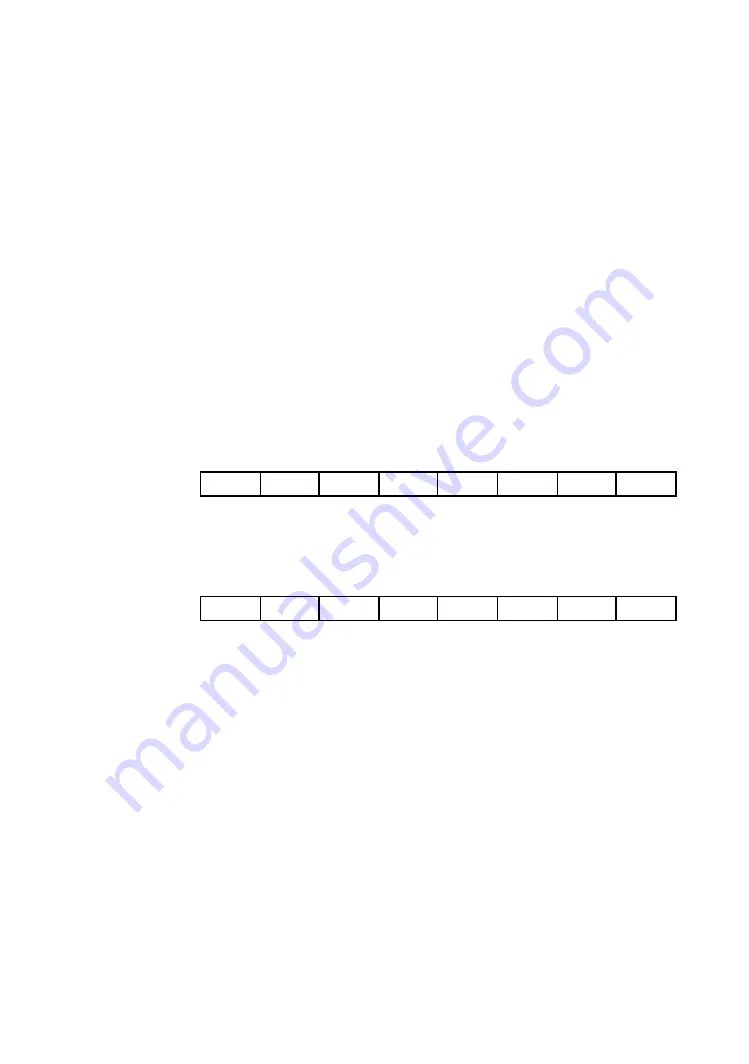

5.3.6

Vector Number Setting Register C (VCRC)

The vector number setting register C (VCRC) is a 16-bit read/write register that sets the FRT

input-capture interrupt and output-compare interrupt vector numbers (0–127). VCRC is initialized

to H'0000 on reset. It is not initialized in standby mode.

Bit:

15

14

13

12

11

10

9

8

Bit name:

—

FICV6

FICV5

FICV4

FICV3

FICV2

FICV1

FICV0

Initial value:

0

0

0

0

0

0

0

0

R/W:

R

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bit:

7

6

5

4

3

2

1

0

Bit name:

—

FOCV6

FOCV5

FOCV4

FOCV3

FOCV2

FOCV1

FOCV0

Initial value:

0

0

0

0

0

0

0

0

R/W:

R

R/W

R/W

R/W

R/W

R/W

R/W

R/W

•

Bits 15, 7—Reserved bits: These bits always read 0. The write value should always be 0.

•

Bits 14 to 8—Free-running timer (FRT) input-capture interrupt vector number (FICV6–

FICV0): These bits set the vector number for the free-running timer (FRT) input-capture

interrupt (ICI). There are seven bits, so the value can be set between 0 and 127.

•

Bits 6 to 0—Free-running timer (FRT) output-compare interrupt vector number (FOCV6–

FOCV0): These bits set the vector number for the free-running timer (FRT) output-compare

interrupt (OCI). There are seven bits, so the value can be set between 0 and 127.

Summary of Contents for SH7095

Page 1: ...SH7095 Hardware User Manual ...

Page 23: ...12 Hitachi ...

Page 63: ...52 Hitachi ...

Page 77: ...66 Hitachi ...

Page 105: ...94 Hitachi Figure 5 14 Pipeline Operation when Interrupts are Enabled by Changing the SR ...

Page 127: ...116 Hitachi ...

Page 152: ...Hitachi 141 Figure 7 8 Example of 32 Bit Data Width SRAM Connection ...

Page 157: ...146 Hitachi Figure 7 13 Synchronous DRAM 32 bit Device Connection ...

Page 161: ...150 Hitachi Figure 7 15 Basic Burst Read Timing Auto Precharge ...

Page 167: ...156 Hitachi Figure 7 20 Burst Read Timing Bank Active Same Row Address ...

Page 168: ...Hitachi 157 Figure 7 21 Burst Read Timing Bank Active Different Row Addresses ...

Page 169: ...158 Hitachi Figure 7 22 Write Timing No Precharge ...

Page 170: ...Hitachi 159 Figure 7 23 Write Timing Bank Active Same Row Address ...

Page 180: ...Hitachi 169 Figure 7 29 Example of a DRAM Connection 32 Bit Data Width ...

Page 190: ...Hitachi 179 Figure 7 36 Example of Pseudo SRAM Connection 1 M pseudo SRAM ...

Page 191: ...180 Hitachi Figure 7 37 Example of Pseudo SRAM Connection 4 M pseudo SRAM ...

Page 209: ...198 Hitachi Figure 7 50 Master and Partial Share Master Connections ...

Page 231: ...220 Hitachi ...

Page 287: ...276 Hitachi ...

Page 307: ...296 Hitachi Note For a CPU writing H AA55 to FRC Figure 11 2 FRC Access Operation Write ...

Page 308: ...Hitachi 297 Note For an FRC reading from a CPU H AA55 Figure 11 3 FRC Access Operation Read ...

Page 333: ...322 Hitachi ...

Page 370: ...Hitachi 359 Figure 13 12 Sample Flowchart for Receiving Multiprocessor Serial Data ...

Page 371: ...360 Hitachi Figure 13 12 Sample Flowchart for Receiving Multiprocessor Serial Data cont ...

Page 395: ...384 Hitachi ...

Page 402: ...Hitachi 391 Figure 15 6 PLL Synchronization Settling Timing ...

Page 408: ...Hitachi 397 Figure 15 13 Bus Release Timing Slave Mode With PLL1 Off ...

Page 436: ...Hitachi 425 Figure 15 33 Synchronous DRAM Mode Register Write Cycle TRP 1 Cycle ...

Page 437: ...426 Hitachi Figure 15 34 Synchronous DRAM Mode Register Write Cycle TRP 2 Cycles ...

Page 449: ...438 Hitachi Figure 15 46 DRAM CAS Before RAS Refresh Cycle TRP 1 Cycle TRAS 2 Cycles PLL On ...

Page 454: ...Hitachi 443 Figure 15 51 DRAM CAS Before RAS Refresh Cycle TRP 1 Cycle TRAS 2 Cycles PLL Off ...

Page 461: ...450 Hitachi Figure 15 58 Pseudo SRAM Auto Refresh Cycle PLL On TRP 1 Cycle TRAS 2 Cycles ...

Page 462: ...Hitachi 451 Figure 15 59 Pseudo SRAM Self Refresh Cycle PLL On TRP 1 Cycle TRAS 2 Cycles ...

Page 467: ...456 Hitachi Figure 15 64 Pseudo SRAM Auto Refresh Cycle PLL Off TRP 1 Cycle TRAS 2 Cycles ...

Page 468: ...Hitachi 457 Figure 15 65 Pseudo SRAM Self Refresh Cycle PLL Off TRP 1 Cycle TRAS 2 Cycles ...

Page 471: ...460 Hitachi Figure 15 68 Interrupt Vector Fetch Cycle PLL On No Waits ...

Page 472: ...Hitachi 461 Figure 15 69 Interrupt Vector Fetch Cycle PLL Off No Waits ...

Page 473: ...462 Hitachi Figure 15 70 Interrupt Vector Fetch Cycle 1 External Wait Cycle ...

Page 474: ...Hitachi 463 Figure 15 71 Address Monitor Cycle ...

Page 490: ...Hitachi 479 B 2 Register Chart ...