Gate control via SW/HW gate, interrupting

SW gate

HW gate

Reaction Counter

edge 0-1

1

Continue

1

edge 0-1

Continue

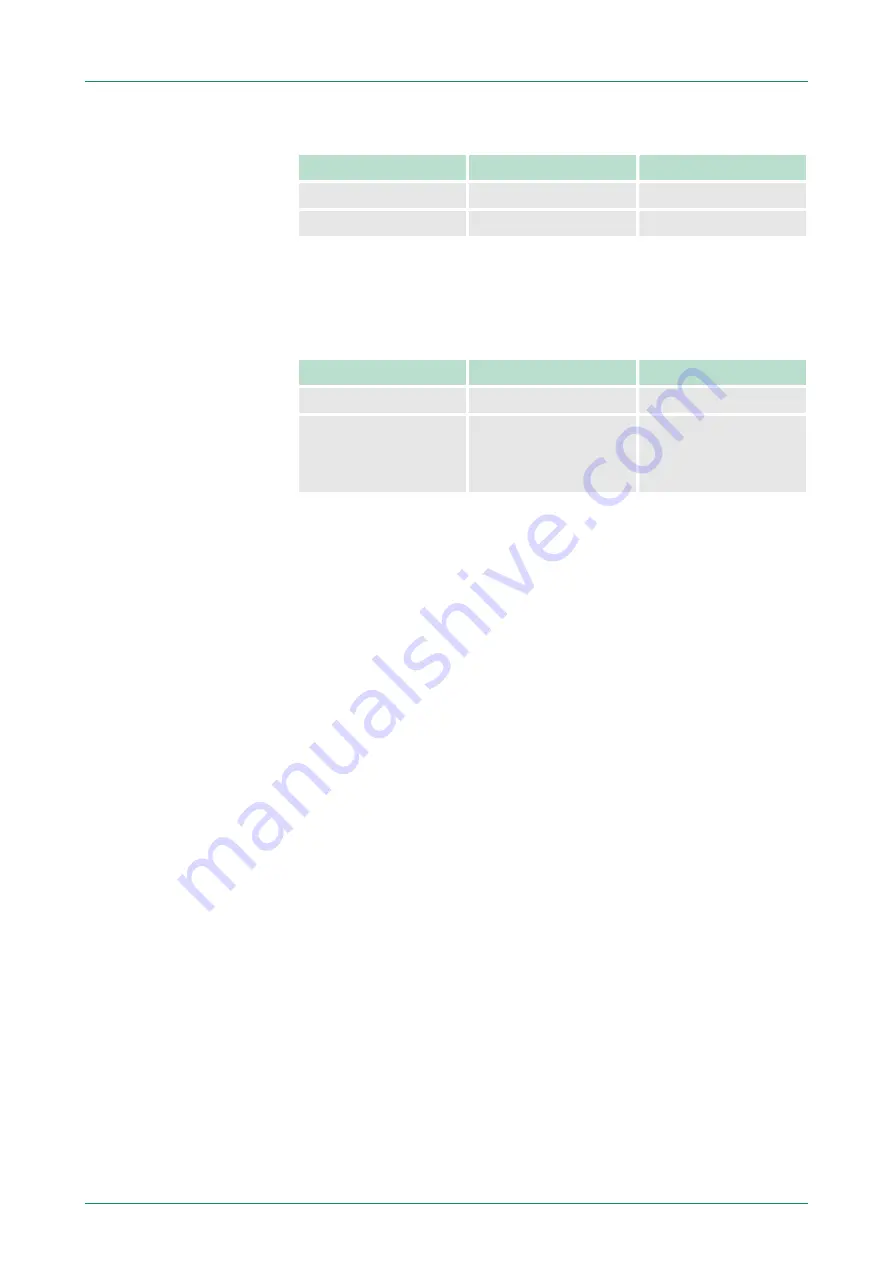

Gate control via

SW/HW gate

, operating mode "Count once": If the

internal gate has been closed automatically it may only be opened

again under the following conditions:

SW gate

HW gate

Reaction I gate

1

edge 0-1

1

edge 0-1

(after edge 0-1

at HW gate)

1

1

As soon as during a count process an edge 0-1 is recognized at the

"Latch" input of the counter, the recent

counter value

is stored in the

latch register. You may access the latch register via the

input area

.

After a STOP-RUN transition latch is always 0.

The

compare value

is to be pre-defined by CC_I. As soon as a com-

parison condition is kept, the bit STS_DO of the counter status is set.

Please consider that the bit STS_DO may only be influenced when in

the

counter status

the bit STS_CTRL_DO is set. You pre-define the

behavior of the counter output via the parameterization (MODE2_I):

n

output never switches

n

output switches when

counter value

³

comparison value

n

output switches when

counter value

£

comparison value

n

output switches at

comparison value

Output never switches

The output never switches.

Output switches when counter value

³

comparison value

The output remains set as long as the

counter value

is higher or

equal

comparison value

.

Output switches when counter value

£

comparison value

The output remains set as long as the counter value is lower or equal

comparison value.

Pulse at comparison value

When the counter reaches the

comparison value

the output is set for

the parameterized

pulse duration

. If the pulse duration = 0 the output

is set until the comparison condition is no longer met. When you've

set a main counting direction the output is only set at reaching the

comparison value

from the main counting direction.

Pulse duration

Gate control "Count

once"

Latch function

Comparison

VIPA System SLIO FM 050

Deployment

Counter additional functions

HB300 | FM | 050-1BA00 | GB | 15-11

56