CHAPTER 4 BCU

Preliminary User’s Manual A14874EJ3V0UM

94

4.9 Data Transfer Using VSB

4.9.1 Data transfer example

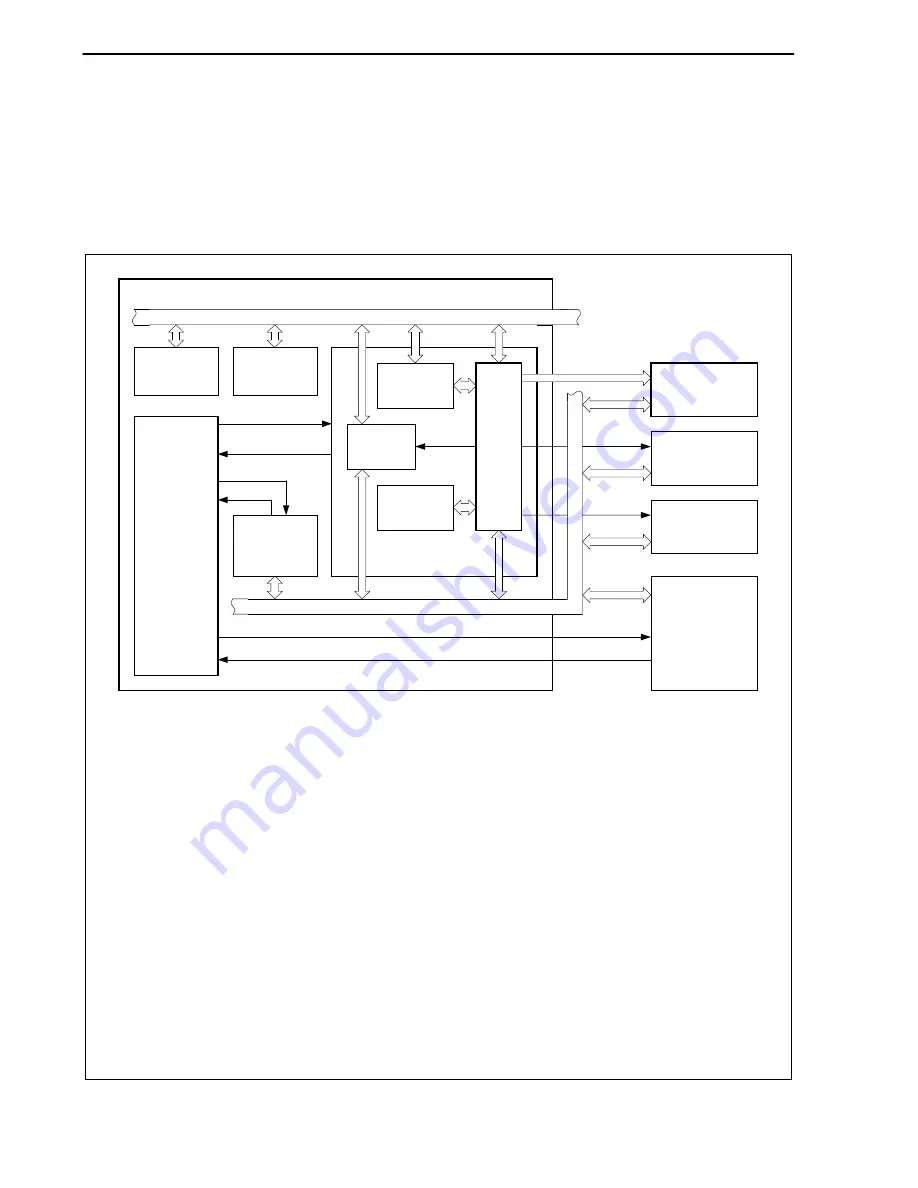

This section uses the circuit shown in Figure 4-13 to explain the procedure for transferring data between bus

masters and bus slaves connected to the VSB.

Figure 4-13. Example of Data Transfer Using VSB

INTC

STBC

CPU

VDSELPZ

VAACK

VAREQ

VAREQ0

VAACK0

VAACK2

<1>

<2>

VSB

NPB

VDCSZ5 to

VDCSZ0

NU85E

<4>

<3>

Bus arbiter

NU85E interior

(Bus master 2)

DMAC

BBR

VDCSZ7

User logic 1

(Bus slave 2)

BCU

Memory controller

(MEMC)

(Bus slave 0)

User logic 0

(Bus slave 1)

VDCSZ6

External circuit

(Bus master 1)

TIC

(Bus master 0)

LOCK

<1> The NU85E grants bus control (bus access right) to only one bus master according to the on-chip bus

arbiter (Refer to

4.9.5 Bus master transition

for detail). The bus arbiter arbitrates the bus access right

according to the following prioritization.

TIC (bus master 0) > External circuit (bus master 1) > NU85E interior (bus master 2)

For example, if a bus access right request (VAREQ) is generated from the TIC or an external circuit when

the NU85E interior is operating as the bus master, the NU85E interior releases the bus.

In the figure shown above, the NU85E interior (bus master 2) receives an acknowledge signal (VAACK2:

internal signal) from the bus arbiter and has the bus access right (A bus access right request signal is

always being output from the NU85E interior to the bus arbiter).

<2> Bus master 2, which has the bus access right, begins the data transfer to the VSB.

<3> The BCU selects the bus slave by generating a chip select signal (VDCSZn) corresponding to each bank

of the data area according to the programmable chip select function (n = 7 to 0). In the figure shown

above, MEMC (bus slave 0) is selected by the VDCSZ5 to VDCSZ0 signals.

<4> The selected bus slave 0 returns a transfer response to bus master 2, and the data transfer begins.