CDJ-800MK2

41

5

6

7

8

5

6

7

8

C

D

F

A

B

E

41

CH1 : DACLRCK

from DAC

V: 5.0 V/div. H: 1 sec/div.

42

CH2 : DACDATA

from DAC

V: 5.0 V/div. H: 1 sec/div.

43

CH3 : DACBCK

from DAC

V: 5.0 V/div. H: 1 sec/div.

44

CH4 : ZERO

to CPU

V: 5.0 V/div. H: 1 sec/div.

Association between zero-data detection and

muting control (1/2)

Audio mute

MAIN ASSY

A

Conditions:

At the time of power on, with a disc loaded

18

CH1 : RST

from CPU Reset IC

V: 2.0 V/div. H: 1 sec/div.

35

CH2 : DAC11M

from AUDIO DSP

V: 5.0 V/div. H: 1 sec/div.

39

CH3 : DACRST

from CPU IC

V: 2.0 V/div. H: 1 sec/div.

40

CH4 : L4 (JACK Assy)

Audio Signal Line

V: 20.0 V/div. H: 1 sec/div.

DAC reset

DAC

39

CH3 : DACRST

from CPU IC

V: 5.0 V/div. H: 200 msec/div.

32

CH5 : CLK

from CPU IC

V: 5.0 V/div. H: 200 msec/div.

26

CH6 : DATA

from CPU IC

V: 5.0 V/div. H: 200 msec/div.

33

CH7 : DACCS

from CPUIC

V: 5.0 V/div. H: 200 msec/div.

Initialization of DAC (downloading using the

common 3-wire serial lines)

DAC

39

CH3 : DACRST

from CPU IC

V: 5.0 V/div. H: 5

µ

sec/div.

32

CH5 : CLK

from CPU IC

V: 2.0 V/div. H: 5

µ

sec/div.

26

CH6 : DATA

from CPU IC

V: 2.0 V/div. H: 5

µ

sec/div.

33

CH7 : DACCS

from CPU IC

V: 2.0 V/div. H: 5

µ

sec/div.

DAC controlled by the MPU (fixed-cycle polling

using the common 3-wire serial lines)

DAC

41

CH1 : DACLRCK

from DAC

V: 5.0 V/div. H: 1 sec/div.

42

CH2 : DACDATA

from DAC

V: 5.0 V/div. H: 1 sec/div.

43

CH3 : DACBCK

from DAC

V: 5.0 V/div. H: 1 sec/div.

44

CH4 : ZERO

to CPU

V: 5.0 V/div. H: 1 sec/div.

Conditions in which muting for zero-data

detection is activated (Standby)

Audio mute

Conditions:

At the time of power on, with a disc loaded

Conditions in which muting for zero-data

detection is activated (pause, continuous search)

Audio mute

41

CH1 : DACLRCK

from DAC

V: 5.0 V/div. H: 1 sec/div.

42

CH2 : DACDATA

from DAC

V: 5.0 V/div. H: 1 sec/div.

43

CH3 : DACBCK

from DAC

V: 5.0 V/div. H: 1 sec/div.

44

CH4 : ZERO

to CPU

V: 5.0 V/div. H: 1 sec/div.

Conditions:

During playback

Conditions in which muting for zero-data

detection is activated (Jog Touch, track search)

Audio mute

41

CH1 : DACLRCK

from DAC

V: 5.0 V/div. H: 1 sec/div.

42

CH2 : DACDATA

from DAC

V: 5.0 V/div. H: 1 sec/div.

43

CH3 : DACBCK

from DAC

V: 5.0 V/div. H: 1 sec/div.

44

CH4 : ZERO

to CPU

V: 5.0 V/div. H: 1 sec/div.

Conditions:

During playback

41

CH1 : DACLRCK

from DAC

V: 5.0 V/div. H: 1 sec/div.

42

CH2 : DACDATA

from DAC

V: 5.0 V/div. H: 1 sec/div.

43

CH3 : DACBCK

from DAC

V: 5.0 V/div. H: 1 sec/div.

44

CH4 : ZERO

to CPU

V: 5.0 V/div. H: 1 sec/div.

Conditions:

During playback

Remarks:

• The MPU polls the audio DSP and DAC in a fixed cycle.

• The intervals of a cycle are 3 msec for playback of a

CD-DA, and 10 msec for playback of a signal for MP3.

44

CH4 : ZERO

to CPU

V: 5.0 V/div. H: 1 sec/div.

45

CH5 : L ch

to JACK Assy

V: 5.0 V/div. H: 1 sec/div.

46

CH6 : MUTE

to JACK Assy

V: 5.0 V/div. H: 1 sec/div.

47

CH7 : L ch (JACK Assy)

V: 5.0 V/div. H: 1 sec/div.

Association between zero-data detection and

muting control (2/2)

Audio mute

Conditions:

At the time of power on, with a disc loaded

Conditions in which muting for zero-data

detection is activated (between musical pieces)

Audio mute

CH1

CH2

CH3

CH4

CH1

CH1

CH2

CH3

CH4

CH1

CH2

CH3

CH4

CH1

CH2

CH3

CH4

CH2

CH3

CH4

CH4

CH5

CH6

CH7

CH1

CH2

CH3

CH4

CH3

CH5

CH6

CH7

CH3

CH5

CH6

CH7

The MPU is started after a specific delay time.

DAC reset

DAC reset

DSP/DAC download

FPGA download

PLAY start

Power ON

Power ON

PLAY start

Power ON

PLAY start

PLAY start

During

pause

7 sec typ

DSP

DAC

Touch the

touch panel

Track search

Between musical pieces

During continuous search

(fast forward)

a - b : 690 msec

b

a

Содержание CDJ-800MK2

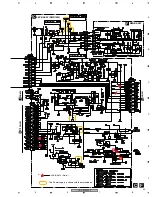

Страница 27: ...CDJ 800MK2 27 5 6 7 8 5 6 7 8 C D F A B E MODE MODE 3 3 A 27 24 26 19 36 ...

Страница 29: ...CDJ 800MK2 29 5 6 7 8 5 6 7 8 C D F A B E Data PANEL DATA Digital A 2 3 3 3 A 3 3 A 23 ...

Страница 119: ...CDJ 800MK2 119 5 6 7 8 5 6 7 8 C D F A B E SCF5249LAG140 MAIN ASSY IC301 32 bit RISC MPU Block Diagram ...

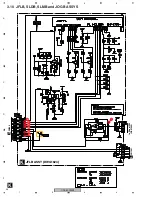

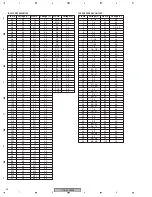

Страница 130: ...CDJ 800MK2 130 1 2 3 4 1 2 3 4 C D F A B E Pin Function ...

Страница 135: ...CDJ 800MK2 135 5 6 7 8 5 6 7 8 C D F A B E Pin Function ...

Страница 138: ...CDJ 800MK2 138 1 2 3 4 1 2 3 4 C D F A B E PE8001A MAIN ASSY IC702 DAC IC Pin Arrangement Top view Block Diagram ...

Страница 139: ...CDJ 800MK2 139 5 6 7 8 5 6 7 8 C D F A B E Pin Function ...

Страница 143: ...CDJ 800MK2 143 5 6 7 8 5 6 7 8 C D F A B E ...

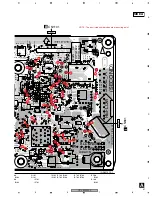

Страница 153: ...CDJ 800 7 5 6 7 8 5 6 7 8 C D F A B E ...

Страница 174: ...CDJ 800 28 1 2 3 4 1 2 3 4 C D F A B E 3 7 JFLB SLDB and JOGB ASSYS I JFLB ASSY DWG1565 I CN500 F ...

Страница 180: ...CDJ 800 34 1 2 3 4 1 2 3 4 C D F A B E ...

Страница 200: ...CDJ 800 54 1 2 3 4 1 2 3 4 C D F A B E 6 ADJUSTMENT There is no information to be shown in this chapter ...