CDJ-800MK2

120

1

2

3

4

1

2

3

4

C

D

F

A

B

E

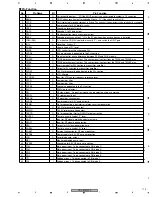

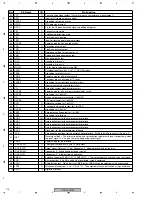

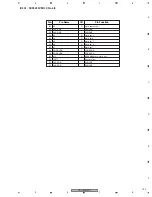

No.

Pin Name

I/O

Pin Function

D4

SCL/QSPI_CLK

I/O

IIC clock/QSPI clock pin function select is

PLLCR(11)

A1

CS0

O

Static chip select 0

D3

A21

O

SDRAM address / static adr

B1

A11

O

SDRAM address / static adr

C2

A10

O

SDRAM address / static adr

C1

A9

O

SDRAM address / static adr

E3

CMD_SDIO2/GPIO34

IO

MemoryStick/SD

D2

A18

O

SDRAM address / static adr

D1

A17

O

SDRAM address / static adr

E2

BCLK/GPIO10

I/O

SDRAM clock output

F3

SCLK_OUT/GPIO15

I/O

MemoryStick/SD

E1

BCLKE

O

SDRAM clock enable output

E4

SDA/QSPI_DIN

I/O

IIC data/QSPI data in function select is

PLLCR(11)

F2

DATA24

I/O

Data bus bit 24

G3

A22

O

SDRAM address / static adr

F1

SDUDQM

O

SDRAM UDQM

F4

EF/GPIO19

IO

Error flag input

G4

SDATA0_SDIO1/GPIO54

I/O

MemoryStick/SD

G1

DATA25

I/O

Data bus bit 25

G2

DATA26

I/O

Data bus bit 26

H3

RSTO/SDATA2_BS2

I/O

Reset output/MemoryStick/SD/

H1

DATA27

I/O

Data bus bit 27

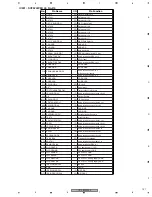

H4

PAD-GND

–

PAD-GND

H4

PAD-GND

–

PAD-GND

H2

DATA28

I/O

Data bus bit 28

J1

DATA29

I/O

Data bus bit 29

J3

SDATA3/GPIO56

IO

SD interface data line

J2

DATA30

I/O

Data bus bit 30

J4

BUFENB1/GPIO57

IO

External buffer 1 enable

K1

DATA31

I/O

Data bus bit 31

K6

CORE-VDD

–

CORE-VDD

K6

CORE-VDD

–

CORE-VDD

K2

A13

O

SDRAM address / static adr

K3

A25/GPO8

O

SDRAM address / static adr

K5

CORE-GND

–

CORE-GND

K5

CORE-GND

–

CORE-GND

K4

A 23

O

SDRAM address / static adr

L1

A14

O

SDRAM address / static adr

L2

A15

O

SDRAM address / static adr

M1

A16

O

SDRAM address / static adr

L3

PAD-VDD

–

PAD-VDD

L3

PAD-VDD

–

PAD-VDD

M2

A19

O

SDRAM address / static adr

N1

A20

O

SDRAM address / static adr

L4

QSPI_CS1/GPIO24

IO

QSPI select 1

M3

TEST2

Structural test

N2

SDRAM_CS1

O

SDRAM chip select out 1

M4

SDATA1_BS1/GPIO9

I/O

MemoryStick/SD

P1

SDRAS

O

SDRAM RAS

P2

SDCAS

O

SDRAM CAS

N3

SDWE

O

SDRAM write enable

P3

SDLDQM

O

SDRAM LDQM

N4

GPIO5

I/O

General purpose i/o

P4

QSPI_CS0/GPIO29

I/O

QSPI chip select 0

N5

QSPI_DOUT/GPIO26

I/O

Qspsi data out

I

Pin Function

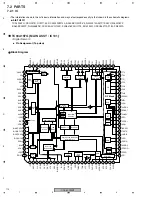

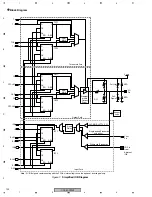

IC301 : SCF5249VM140

_No.1/4

Содержание CDJ-800MK2

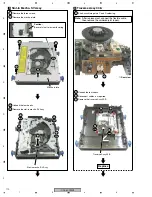

Страница 27: ...CDJ 800MK2 27 5 6 7 8 5 6 7 8 C D F A B E MODE MODE 3 3 A 27 24 26 19 36 ...

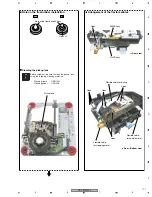

Страница 29: ...CDJ 800MK2 29 5 6 7 8 5 6 7 8 C D F A B E Data PANEL DATA Digital A 2 3 3 3 A 3 3 A 23 ...

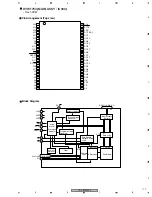

Страница 119: ...CDJ 800MK2 119 5 6 7 8 5 6 7 8 C D F A B E SCF5249LAG140 MAIN ASSY IC301 32 bit RISC MPU Block Diagram ...

Страница 130: ...CDJ 800MK2 130 1 2 3 4 1 2 3 4 C D F A B E Pin Function ...

Страница 135: ...CDJ 800MK2 135 5 6 7 8 5 6 7 8 C D F A B E Pin Function ...

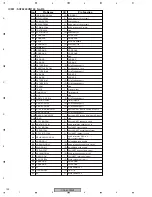

Страница 138: ...CDJ 800MK2 138 1 2 3 4 1 2 3 4 C D F A B E PE8001A MAIN ASSY IC702 DAC IC Pin Arrangement Top view Block Diagram ...

Страница 139: ...CDJ 800MK2 139 5 6 7 8 5 6 7 8 C D F A B E Pin Function ...

Страница 143: ...CDJ 800MK2 143 5 6 7 8 5 6 7 8 C D F A B E ...

Страница 153: ...CDJ 800 7 5 6 7 8 5 6 7 8 C D F A B E ...

Страница 174: ...CDJ 800 28 1 2 3 4 1 2 3 4 C D F A B E 3 7 JFLB SLDB and JOGB ASSYS I JFLB ASSY DWG1565 I CN500 F ...

Страница 180: ...CDJ 800 34 1 2 3 4 1 2 3 4 C D F A B E ...

Страница 200: ...CDJ 800 54 1 2 3 4 1 2 3 4 C D F A B E 6 ADJUSTMENT There is no information to be shown in this chapter ...