CDJ-800MK2

122

1

2

3

4

1

2

3

4

C

D

F

A

B

E

No.

Pin Name

I/O

Pin Function

G11 IDE-IORDY/GPIO16

I/O

IDE IORDY

G14 MCLK1/GPO39

O

Audio master clock output 1

G12 SUBR/GPIO53

IO

Subcode data

G13 MCLK2/GPO42

O

Audio master clock output 2

F14

XTRIM/GPO38

O

Audio interfaces X-tal trim

F11

TRST/DSCLK

I

Jtag

F13

SFSY/GPIO52

IO

Subcode sync

E9

CORE-VDD

–

CORE-VDD

E9

CORE-VDD

–

CORE-VDD

E14

RW_B

O

Bus write enable

F12

RCK/GPIO 51

IO

Subcode clock

E13

TMS/BKPT

I

Jtag

E10

CORE-GND

–

CORE-GND

E10

CORE-GND

–

CORE-GND

E12

TCK

I

Jtag

E11

PAD-GND

–

PAD-GND

E11

PAD-GND

–

PAD-GND

D14

PST3/GPIO 62

IO

ColdFire debug port

D13

CNPSTCLK/GPO 63

O

Coldfire debug clock

C14

PST1/GPIO 60

IO

ColdFire debug port

D12

PAD-VDD

–

PAD-VDD

D12

PAD-VDD

–

PAD-VDD

C13

PST2/GPIO 61

IO

ColdFire debug port

B14

PST0/GPIO 59

IO

ColdFire debug port

D11

TDI/DSI

I

Jtag

C12

TEST0

I

Structural test

B13

TIN0/GPI33

i

Timer input 0

C11

Hl-Z

I

Jtag

A14

DDATA 3 / GPIO 4

IO

ColdFire debug port

A13

TOUT0 / GPO33

O

Timer output 0

B12

DDATA1/GPIO 1

IO

ColdFire debug port

A12

DDATA2/GPIO 2

IO

ColdFire debug port

B11

CTS2_B / ADIN3/GP131

I

Second UART clear to send, AD input 3

A11

DDATA0/GPIO 0

IO

ColdFire debug port

B10

RXD2 / GPI28/ADIN2

I

Second UART receive data input AD input 2

D10

TDSO

O

Jtag

A10

RTS2_B/GPO31

O

Second UART request to send

B9

SDATAI3 / GPI 41

I

audio interfaces serial data 3 in

D9

CTS1_B/GPI30

I

First UART clear to send

A9

TXD2/GPO28

O

Second UART transmit data output

D8

RTS1_B / GPO30

O

First UART request to send

A8

EBUIN4/ADIN1/GPI 39

I

audio interfaces EBU in 4/

AD convertor input 1

E8

SRE/GPIO11

IO

SmartMedia read enable

B8

LRCK3 / GPIO 45

IO

Audio interfaces serial word clock 3

E7

SWE/GPI012

IO

SmartMedia write enable

D7

TXD1/GPO27

O

First UART transmit data output

A7

SCLK3/GPIO49

IO

Audio interfaces serial clock 3

B7

RXD1 / GPI27

I

First UART receive data input

A6

CS1 / GPIO58

IO

Static chip select l / gpio l

E6

CORE-GND

–

CORE-GND

E6

CORE-GND

–

CORE-GND

B6

A1

O

Static address A1

D6

TIN1/GP1O23

IO

Timer l in

A5

A2

O

Static address A2

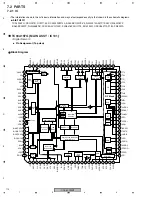

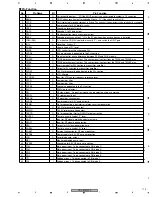

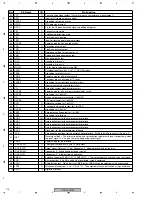

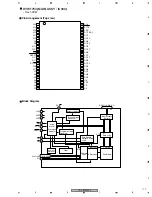

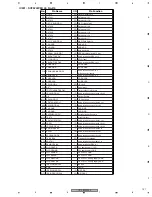

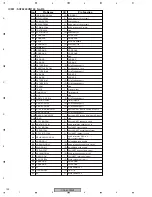

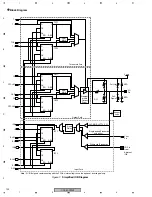

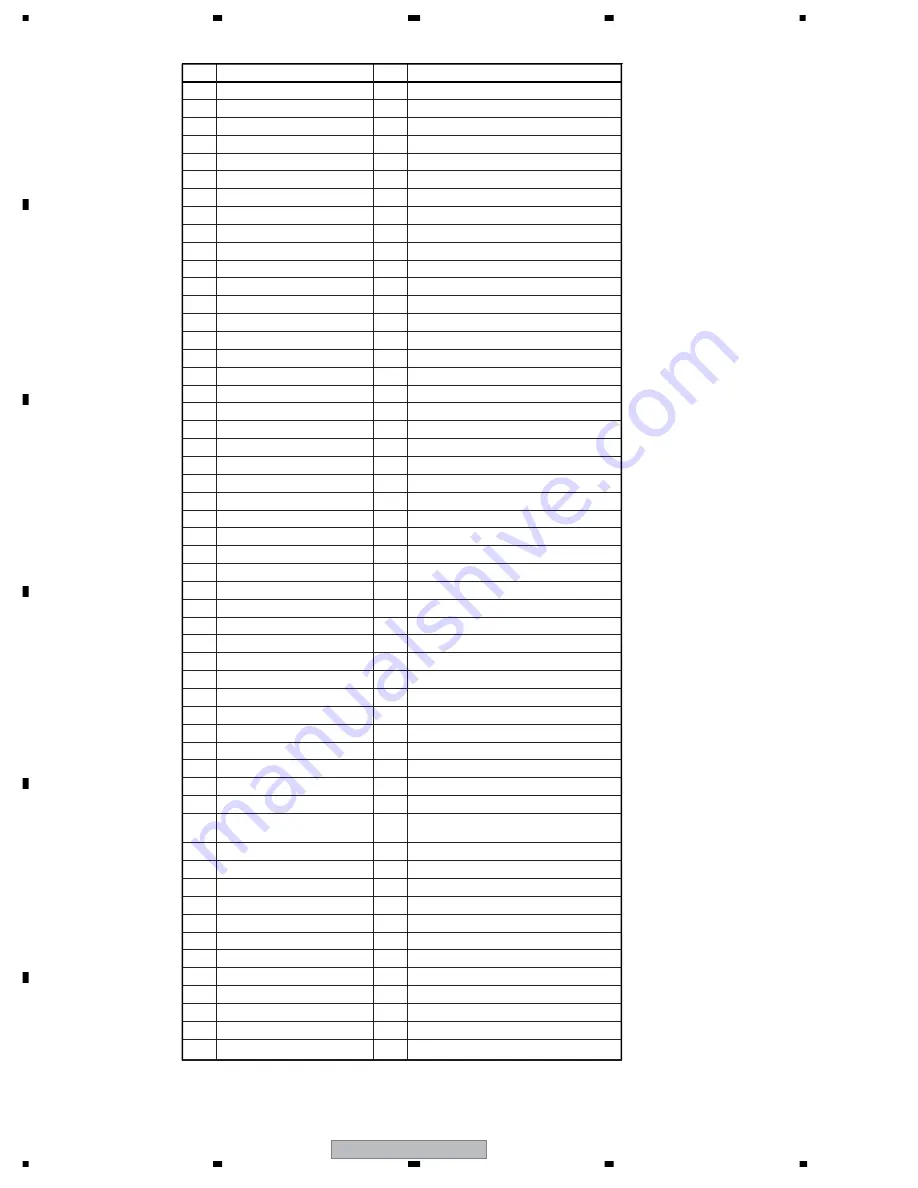

IC301 : SCF5249VM140_No.3/4

Содержание CDJ-800MK2

Страница 27: ...CDJ 800MK2 27 5 6 7 8 5 6 7 8 C D F A B E MODE MODE 3 3 A 27 24 26 19 36 ...

Страница 29: ...CDJ 800MK2 29 5 6 7 8 5 6 7 8 C D F A B E Data PANEL DATA Digital A 2 3 3 3 A 3 3 A 23 ...

Страница 119: ...CDJ 800MK2 119 5 6 7 8 5 6 7 8 C D F A B E SCF5249LAG140 MAIN ASSY IC301 32 bit RISC MPU Block Diagram ...

Страница 130: ...CDJ 800MK2 130 1 2 3 4 1 2 3 4 C D F A B E Pin Function ...

Страница 135: ...CDJ 800MK2 135 5 6 7 8 5 6 7 8 C D F A B E Pin Function ...

Страница 138: ...CDJ 800MK2 138 1 2 3 4 1 2 3 4 C D F A B E PE8001A MAIN ASSY IC702 DAC IC Pin Arrangement Top view Block Diagram ...

Страница 139: ...CDJ 800MK2 139 5 6 7 8 5 6 7 8 C D F A B E Pin Function ...

Страница 143: ...CDJ 800MK2 143 5 6 7 8 5 6 7 8 C D F A B E ...

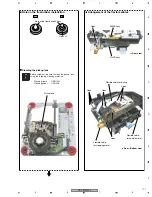

Страница 153: ...CDJ 800 7 5 6 7 8 5 6 7 8 C D F A B E ...

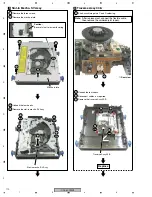

Страница 174: ...CDJ 800 28 1 2 3 4 1 2 3 4 C D F A B E 3 7 JFLB SLDB and JOGB ASSYS I JFLB ASSY DWG1565 I CN500 F ...

Страница 180: ...CDJ 800 34 1 2 3 4 1 2 3 4 C D F A B E ...

Страница 200: ...CDJ 800 54 1 2 3 4 1 2 3 4 C D F A B E 6 ADJUSTMENT There is no information to be shown in this chapter ...