CDJ-800MK2

39

5

6

7

8

5

6

7

8

C

D

F

A

B

E

11

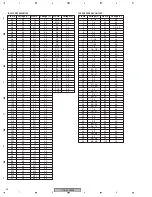

CH1 : TE

V: 1.0 V/div. H: 1 msec/div.

14

CH2 : TRO

V: 1.0 V/div. H: 1 msec/div.

1

CH3 : RFO

V: 1.0 V/div. H: 1 msec/div.

17

CH4 : SBOK

V: 5.0 V/div. H: 1 msec/div.

11

CH1 : TE

V: 1.0 V/div. H: 2 msec/div.

14

CH2 : TRO

V: 1.0 V/div. H: 2 msec/div.

1

CH3 : RFO

V: 1.0 V/div. H: 2 msec/div.

17

CH4 : SBOK

V: 5.0 V/div. H: 2 msec/div.

Pause

Scan (1/2)

11

CH1 : TE

V: 1.0 V/div. H: 50 msec/div.

14

CH2 : TRO

V: 1.0 V/div. H: 50 msec/div.

1

CH3 : RFO

V: 1.0 V/div. H: 50 msec/div.

17

CH4 : SBOK

V: 5.0 V/div. H: 50 msec/div.

Track search (1/2)

8

CH1 : FE

V: 1.0 V/div. H: 50 msec/div.

11

CH2 : TE

V: 1.0 V/div. H: 50 msec/div.

15

CH3 : SL1IN

V: 1.0 V/div. H: 50 msec/div.

16

CH4 : SL2IN

V: 1.0 V/div. H: 50 msec/div.

Track search (2/2)

8

CH1 : FE

V: 1.0 V/div. H: 50 msec/div.

11

CH2 : TE

V: 1.0 V/div. H: 50 msec/div.

15

CH3 : SL1IN

V: 1.0 V/div. H: 50 msec/div.

16

CH4 : SL2IN

V: 1.0 V/div. H: 50 msec/div.

Scan (2/2)

8

CH1 : FE

V: 1.0 V/div. H: 200 msec/div.

11

CH2 : TE

V: 1.0 V/div. H: 200 msec/div.

12

CH3 : DMO

V: 2.0 V/div. H: 200 msec/div.

13

CH4 : LDO

V: 2.0 V/div. H: 200 msec/div.

Stop

8

CH1 : FE

V: 1.0 V/div. H: 500 msec/div.

9

CH2 : FOO

V: 1.0 V/div. H: 500 msec/div.

11

CH3 : TE

V: 1.0 V/div. H: 500 msec/div.

14

CH4 : TRO

V: 2.0 V/div. H: 500 msec/div.

Auto adjust

8

CH1 : FE

V: 1.0 V/div. H: 500 msec/div.

11

CH2 : TE

V: 1.0 V/div. H: 500 msec/div.

15

CH3 : SL1IN

V: 1.0 V/div. H: 500 msec/div.

16

CH4 : SL2IN

V: 1.0 V/div. H: 500 msec/div.

Play

CD player

CD player

CD player

CD player

CD player

CD player

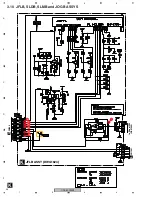

18

CH1 : RST

from Reset IC to CPU

V: 5.0 V/div. H: 200 msec/div.

19

CH2 : PRGM

from CPU to FPGA through IC312

V: 5.0 V/div. H: 200 msec/div.

20

CH3 : SRVRST

from CPU to IC101

V: 5.0 V/div. H: 200 msec/div.

21

CH4 : DSPRST

from CPU to IC701

V: 5.0 V/div. H: 200 msec/div.

Reset system in the core block

CD player

CD player

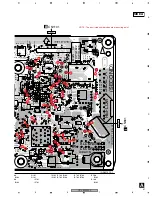

MAIN ASSY

A

Conditions:

At the time of power on,

without a disc loaded

CH1

CH1

CH1

CH1

CH2

CH3

CH4

CH2

CH3

CH4

CH2

CH3

CH4

CH1

CH1

CH2

CH3

CH4

CH2

CH3

CH4

CH2

CH3

CH4

CH1

CH1

CH1

CH2

CH3

CH4

CH2

CH3

CH4

CH2

CH3

CH4

Reset clear

a - b : 370 msec

a - c : 636 msec

a -d : 1 182 msec

e - a : 70 msec

3.3 V

a

b

d

e

c

3.3 V

3.3 V

3.3 V

Содержание CDJ-800MK2

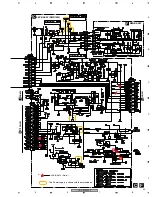

Страница 27: ...CDJ 800MK2 27 5 6 7 8 5 6 7 8 C D F A B E MODE MODE 3 3 A 27 24 26 19 36 ...

Страница 29: ...CDJ 800MK2 29 5 6 7 8 5 6 7 8 C D F A B E Data PANEL DATA Digital A 2 3 3 3 A 3 3 A 23 ...

Страница 119: ...CDJ 800MK2 119 5 6 7 8 5 6 7 8 C D F A B E SCF5249LAG140 MAIN ASSY IC301 32 bit RISC MPU Block Diagram ...

Страница 130: ...CDJ 800MK2 130 1 2 3 4 1 2 3 4 C D F A B E Pin Function ...

Страница 135: ...CDJ 800MK2 135 5 6 7 8 5 6 7 8 C D F A B E Pin Function ...

Страница 138: ...CDJ 800MK2 138 1 2 3 4 1 2 3 4 C D F A B E PE8001A MAIN ASSY IC702 DAC IC Pin Arrangement Top view Block Diagram ...

Страница 139: ...CDJ 800MK2 139 5 6 7 8 5 6 7 8 C D F A B E Pin Function ...

Страница 143: ...CDJ 800MK2 143 5 6 7 8 5 6 7 8 C D F A B E ...

Страница 153: ...CDJ 800 7 5 6 7 8 5 6 7 8 C D F A B E ...

Страница 174: ...CDJ 800 28 1 2 3 4 1 2 3 4 C D F A B E 3 7 JFLB SLDB and JOGB ASSYS I JFLB ASSY DWG1565 I CN500 F ...

Страница 180: ...CDJ 800 34 1 2 3 4 1 2 3 4 C D F A B E ...

Страница 200: ...CDJ 800 54 1 2 3 4 1 2 3 4 C D F A B E 6 ADJUSTMENT There is no information to be shown in this chapter ...