309

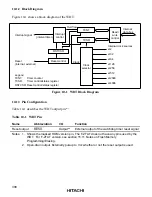

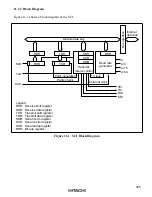

10.1.4 Register Configuration

Table 10-2 summarizes the WDT registers.

Table 10-2 WDT Registers

Address

*

1

Write

*

2

Read

Name

Abbreviation

R/W

Initial Value

H'FFA8

H'FFA8

Timer control/status

register

TCSR

R/(W)

*

3

H'18

H'FFA9

Timer counter

TCNT

R/W

H'00

H'FFAA

H'FFAB

Reset control/status

register

RSTCSR

R/(W)

*

3

H'3F

Notes: 1. Lower 16 bits of the address.

2. Write word data starting at this address.

3. Only 0 can be written in bit 7 to clear the flag.