465

15.7.4

Erase Mode

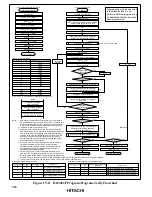

To erase an individual flash memory block, follow the erase/erase-verify flowchart (single-block

erase) shown in figure 15.12.

To perform data or program erasure, make a 1-bit setting for the flash memory area to be erased in

erase block register 1 or 2 (EBR1, EBR2) at least (t

sswe

)

µ

s after setting the SWE bit to 1 in flash

memory control register 1 (FLMCR1). Next, set up the watchdog timer to prevent overerasing in

the event of program runaway, etc. Set a value greater than (t

se

) ms + (t

sesu

+ t

ce

+ t

cesu

)

µ

s as the

WDT overflow period. After this, preparation for erase mode (erase setup) is carried out by setting

the ESU bit in FLMCR1, and after the elapse of (t

cesu

)

µ

s or more, the operating mode is switched

to erase mode by setting the E bit in FLMCR1. The time during which the E bit is set is the flash

memory erase time. Ensure that the erase time does not exceed (t

se

) ms.

Note:

With flash memory erasing, preprogramming (setting all memory data in the memory to

be erased to all "0") is not necessary before starting the erase procedure.

15.7.5

Erase-Verify Mode

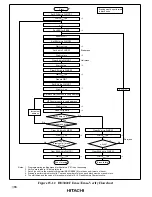

In erase-verify mode, data is read after memory has been erased to check whether it has been

correctly erased.

After the elapse of a the erase time, erase mode is exited (the E bit in FLMCR1 is cleared, then the

ESU bit is cleared at least (t

ce

)

µ

s later), the watchdog timer is cleared, and the operating mode is

switched to erase-verify mode by setting the EV bit in FLMCR. Before reading in erase-verify

mode, a dummy write of H'FF data should be made to the addresses to be read. The dummy write

should be executed after the elapse of (t

sev

)

µ

s or more. When the flash memory is read in this state

(verify data is read in 16-bit units), the data at the latched address is read. Wait at least (t

sevr

)

µ

s

after the dummy write before performing this read operation. If the read data has been erased (all

"1"), a dummy write is performed to the next address, and erase-verify is performed. If the read

data is unerased, set erase mode again and repeat the erase/erase-verify sequence in the same way.

However, ensure that the erase/erase-verify sequence is not repeated more than (N) times. When

verification is completed, exit erase-verify mode, and wait for at least (t

cev

)

µ

s. If erasure has been

completed on all the erase blocks, clear the SWE bit in FLMCR1. If there are any unerased blocks,

make a 1 bit setting for the flash memory area to be erased, and repeat the erase/erase-verify

sequence as before.

Leave a wait time of at least (t

cswe

)

µ

s after clearing SWE.