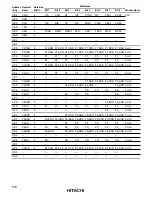

573

Address Register

Data Bus

Bit Names

(low)

Name

Width

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Module Name

H'A0

TPMR

8

—

—

—

—

G3NOV

G2NOV

G1NOV

G0NOV

TPC

H'A1

TPCR

8

G3CMS1 G3CMS0 G2CMS1 G2CMS0 G1CMS1 G1CMS0 G0CMS1 G0CMS0

H'A2

NDERB

8

NDER15 NDER14 NDER13 NDER12 NDER11 NDER10 NDER9

NDER8

H'A3

NDERA

8

NDER7

NDER6

NDER5

NDER4

NDER3

NDER2

NDER1

NDER0

H'A4

NDRB

*

1

8

NDR15

NDR14

NDR13

NDR12

NDR11

NDR10

NDR9

NDR8

8

NDR15

NDR14

NDR13

NDR12

—

—

—

—

H'A5

NDRA

*

1

8

NDR7

NDR6

NDR5

NDR4

NDR3

NDR2

NDR1

NDR0

8

NDR7

NDR6

NDR5

NDR4

—

—

—

—

H'A6

NDRB

*

1

8

—

—

—

—

—

—

—

—

8

—

—

—

—

NDR11

NDR10

NDR9

NDR8

H'A7

NDRA

*

1

8

—

—

—

—

—

—

—

—

8

—

—

—

—

NDR3

NDR2

NDR1

NDR0

H'A8

TCSR

*

2

8

OVF

WT/

IT

TME

—

—

CKS2

CKS1

CKS0

WDT

H'A9

TCNT

*

2

8

H'AA

—

—

—

—

—

—

—

—

—

H'AB

RSTCSR

*

2

8

WRST

RSTOE

—

—

—

—

—

—

H'AC

—

—

—

—

—

—

—

—

—

H'AD

—

—

—

—

—

—

—

—

—

H'AE

—

—

—

—

—

—

—

—

—

H'AF

—

—

—

—

—

—

—

—

—

H'B0

SMR

8

C/

A

CHR

PE

O/

E

STOP

MP

CKS1

CKS0

SCI0

H'B1

BRR

8

H'B2

SCR

8

TIE

RIE

TE

RE

MPIE

TEIE

CKE1

CKE0

H'B3

TDR

8

H'B4

SSR

8

TDRE

RDRF

ORER

FER

PER

TEND

MPB

MPBT

H'B5

RDR

8

H'B6

SCMR

8

—

—

—

—

SDIR

SINV

—

SMIF

Smart card

interface

H'B7

Notes: 1. The address depends on the output trigger setting.

2. For write access to TCSR, TCNT, and RSTCSR, see section 10.2.4, Notes on Register

Access.

Legend

TPC:

Programmable timing pattern controller

WDT: Watchdog timer

SCI:

Serial communication interface