308

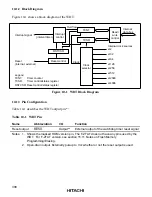

10.1.2 Block Diagram

Figure 10-1 shows a block diagram of the WDT.

ø/2

ø/32

ø/64

ø/128

ø/256

ø/512

ø/2048

ø/4096

TCNT

TCSR

RSTCSR

Reset control

Interrupt signal

Reset

(internal, external)

(interval timer)

Interrupt

control

Overflow

Clock

Clock

selector

Read/

write

control

Internal

data bus

Internal clock sources

Legend

TCNT:

TCSR:

RSTCSR:

Timer counter

Timer control/status register

Reset control/status register

Figure 10-1 WDT Block Diagram

10.1.3 Pin Configuration

Table 10-1 describes the WDT output pin.*

1

Table 10-1 WDT Pin

Name

Abbreviation

I/O

Function

Reset output

RESO

Output

*

2

External output of the watchdog timer reset signal

Notes: 1. Shows the masked ROM version pin. The F-ZTAT does not have any pins used by the

WDT. For F-ZTAT version, see section 15.11 Notes on Flash Memory

Programming/Erasing.

2. Open-drain output. Externally pull-up to Vcc whether or not the reset output is used