145

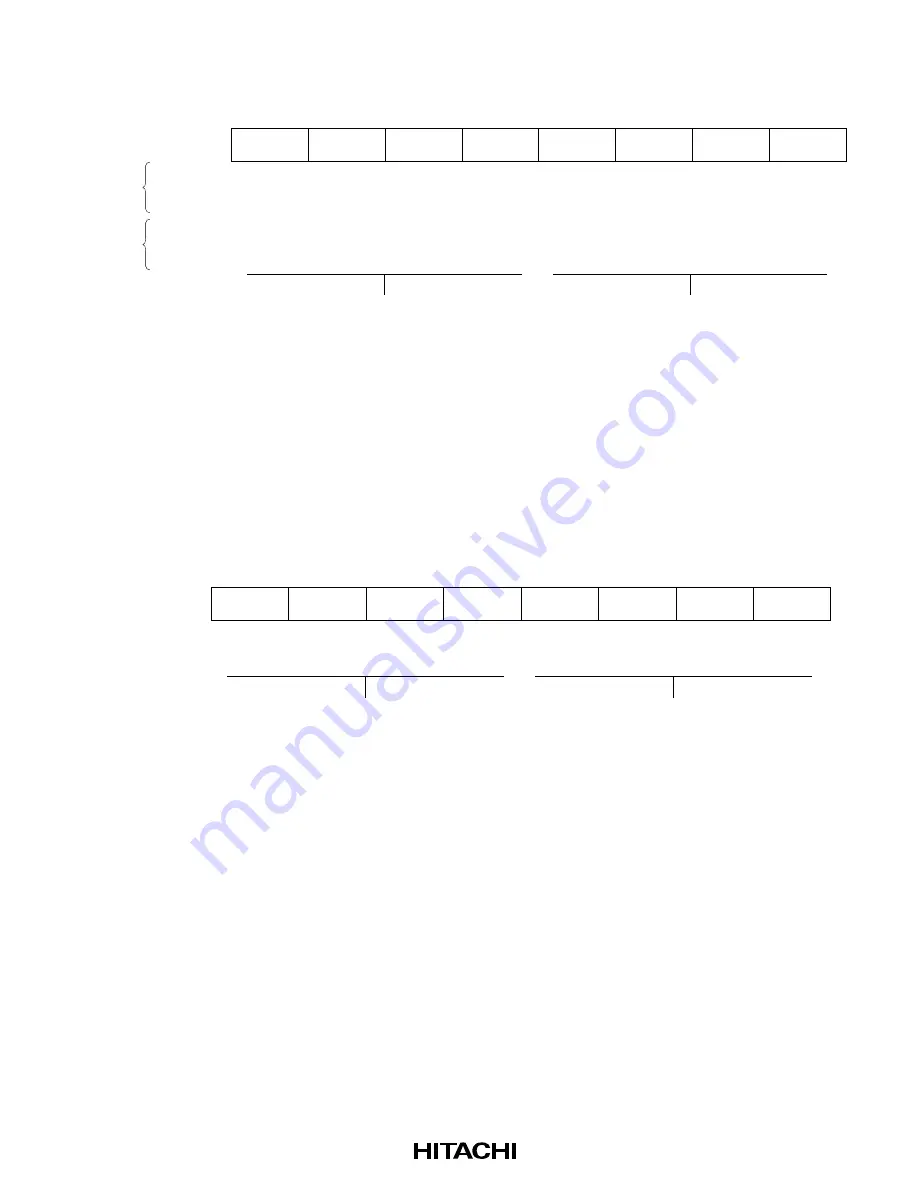

Port 5 Data Direction Register (P5DDR): P5DDR is an 8-bit write-only register that can select

input or output for each pin in port 5.

Bit

Modes

1 and 3

Initial value

Read/Write

Initial value

Read/Write

Modes

5 to 7

7

—

1

—

1

—

6

—

1

—

1

—

5

—

1

—

1

—

4

—

1

—

1

—

3

P5 DDR

1

—

0

W

3

2

P5 DDR

1

—

0

W

2

1

P5 DDR

1

—

0

W

1

0

P5 DDR

1

—

0

W

0

Reserved bits

Port 5 data direction 3 to 0

These bits select input or

output for port 5 pins

P5DDR is initialized to H'F0 by a reset and in hardware standby mode. In software standby mode

it retains its previous setting. If a P5DDR bit is set to 1, the corresponding pin maintains its output

state in software standby mode.

Port 5 Data Register (P5DR): P5DR is an 8-bit readable/writable register that stores data for pins

P5

3

to P5

0

.

Bit

Initial value

Read/Write

7

—

1

—

6

—

1

—

5

—

1

—

4

—

1

—

3

P5

0

R/W

3

2

P5

0

R/W

2

1

P5

0

R/W

1

0

P5

0

R/W

0

Reserved bits

These bits store data

for port 5 pins

Port 5 data 3 to 0

When a bit in P5DDR is set to 1, if port 5 is read the value of the corresponding P5DR bit is

returned directly, regardless of the actual state of the pin. When a bit in P5DDR is cleared to 0, if

port 5 is read the corresponding pin level is read.

Bits P5

7

to P5

4

are reserved. They cannot be modified and are always read as 1.

P5DR is initialized to H'F0 by a reset and in hardware standby mode. In software standby mode it

retains its previous setting.