683

APPENDIX C Timing Diagrams in Flash Memory Mode

■

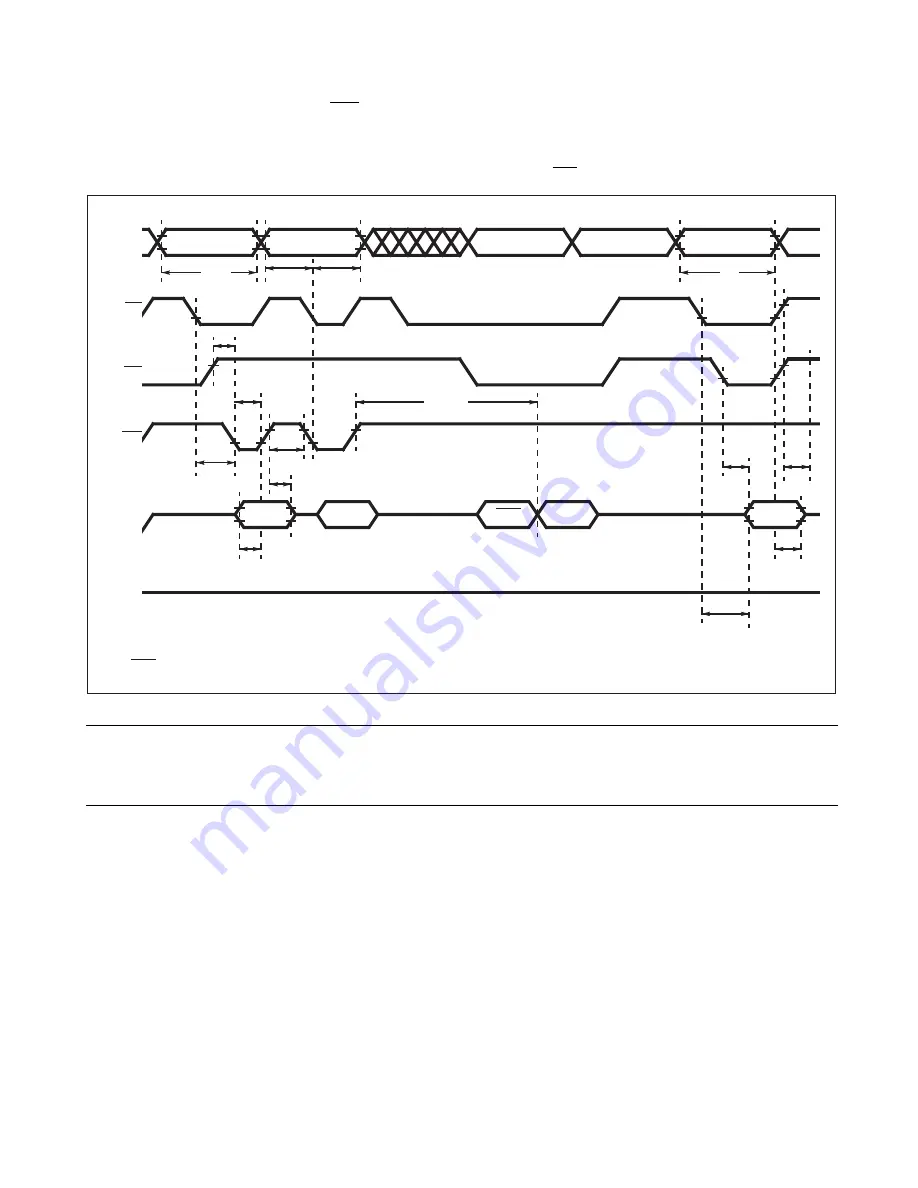

Write, Data Polling, Read (WE Control)

Figure C-2 Write, Data Polling, Read (WE Control)

Note:

The last two bus cycle sequences out of the four are described.

7AAAA

H

t

WC

Third bus cycle

PA

t

AS

t

AH

PA

t

WHWH1

t

WP

t

GHWL

t

CS

t

WPH

t

DH

t

DS

A0

H

PD

DQ7

D

OUT

t

OH

t

DF

t

CE

t

OE

Data polling

PA: Write

address

PD: Write

data

DQ7: Reverse

output

of

w

rite data

D

OUT

: Output

of

w

rite data

t

RC

AQ18

to

AQ0

CE

OE

WE

DQ7

to

DQ0

5.0 V

Содержание MB90390 Series

Страница 2: ......

Страница 4: ......

Страница 17: ...xiii APPENDIX D List of Interrupt Vectors 690 INDEX 695 ...

Страница 18: ...xiv ...

Страница 132: ...104 CHAPTER 5 CLOCKS ...

Страница 152: ...124 CHAPTER 6 CLOCK MODULATOR ...

Страница 210: ...182 CHAPTER 11 TIME BASE TIMER ...

Страница 218: ...190 CHAPTER 12 WATCHDOG TIMER ...

Страница 264: ...236 CHAPTER 14 16 BIT RELOAD TIMER WITH EVENT COUNT FUNCTION ...

Страница 274: ...246 CHAPTER 15 WATCH TIMER ...

Страница 306: ...278 CHAPTER 17 DTP EXTERNAL INTERRUPTS ...

Страница 338: ...310 CHAPTER 18 8 10 BIT A D CONVERTER ...

Страница 364: ...336 CHAPTER 19 UART0 UART1 ...

Страница 398: ...370 CHAPTER 20 UART2 UART3 Figure 20 5 2 ORE Set Timing Receive data RDRF ORE ...

Страница 432: ...404 CHAPTER 20 UART2 UART3 ...

Страница 482: ...454 CHAPTER 22 SERIAL I O ...

Страница 560: ...532 CHAPTER 24 STEPPING MOTOR CONTROLLER ...

Страница 582: ...554 CHAPTER 27 ROM MIRRORING MODULE ...

Страница 632: ...604 CHAPTER 29 EXAMPLES OF SERIAL PROGRAMMING CONNECTION ...

Страница 722: ...694 APPENDIX ...

Страница 723: ...695 INDEX The index follows on the next page This is listed in alphabetic order ...

Страница 740: ......