Real-Time Clock

20-6

Élan™SC520 Microcontroller User’s Manual

microcontroller’s programmable interrupt inputs and program the interrupt steering logic to

route the request to interrupt priority P8.

Disabling the internal RTC does not disable or reset the core in any way.

See “Disabling Internal Peripherals” on page 3-21 for more information.

20.4

REGISTERS

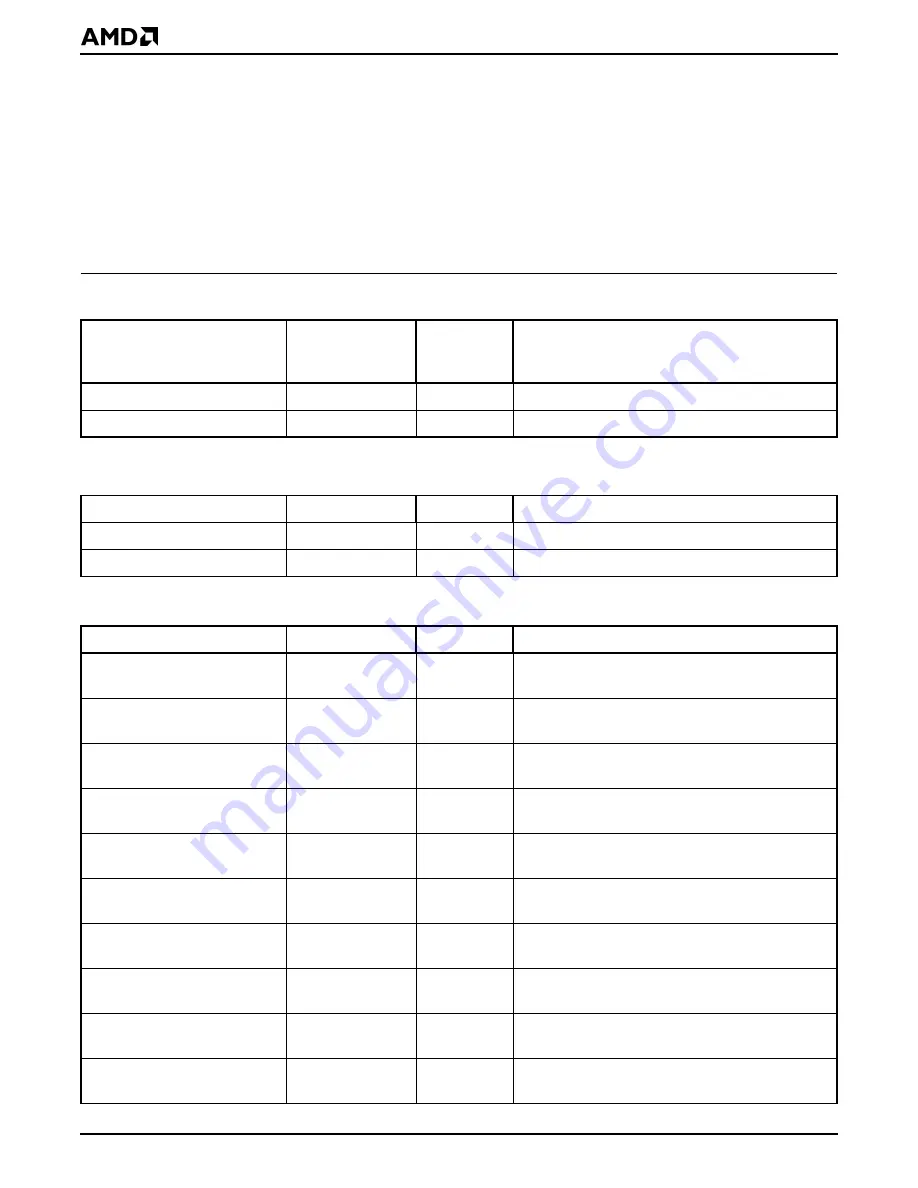

The RTC is controlled by the configuration registers listed in Table 20-1, Table 20-2, and

Table 20-3.

Table 20-1

Real-Time Clock Registers—Memory-Mapped

Register

Mnemonic

MMCR

Offset

Address

Function

Address Decode Control

ADDDECCTL

80h

RTC disable

RTC Interrupt Mapping

RTCMAP

D43h

RTC interrupt mapping

Table 20-2

Real-Time Clock Registers—Direct-Mapped

Register

Mnemonic

I/O Address Function

RTC/CMOS RAM Index

RTCIDX

0070h

RTC index to read or write

RTC/CMOS RAM Data Port

RTCDATA

0071h

Data to be read or written

Table 20-3

Real-Time Clock Registers—RTC Indexed

Register

Mnemonic

I/O Address Function

RTC Current Second

RTCCURSEC

70h/71h

Index 00h

Seconds

RTC Alarm Second

RTCALMSEC

70h/71h

Index 01h

Seconds alarm

RTC Current Minute

RTCCURMIN

70h/71h

Index 02h

Minutes

RTC Alarm Minute

RTCALMMIN

70h/71h

Index 03h

Minutes alarm

RTC Current Hour

RTCCURHR

70h/71h

Index 04h

Hours, 12- and 24-hour mode

RTC Alarm Hour

RTCALMHR

70h/71h

Index 05h

Hours alarm, 12- and 24-hour mode

RTC Current Day of the Week RTCCURDOW

70h/71h

Index 06h

Day of the week

RTC Current Day of the

Month

RTCCURDOM

70h/71h

Index 07h

Day of the month

RTC Current Month

RTCCURMON

70h/71h

Index 08h

Month

RTC Current Year

RTCCURYR

70h/71h

Index 09h

Year

Содержание Elan SC520

Страница 1: ...lan SC520 Microcontroller User s Manual Order 22004A...

Страница 4: ...iv lan SC520 Microcontroller User s Manual...

Страница 28: ...Introduction xxviii lan SC520 Microcontroller User s Manual...

Страница 42: ...Architectural Overview 1 14 lan SC520 Microcontroller User s Manual...

Страница 78: ...System Initialization 3 22 lan SC520 Microcontroller User s Manual...

Страница 108: ...Clock Generation and Control 5 10 lan SC520 Microcontroller User s Manual...

Страница 118: ...Reset Generation 6 10 lan SC520 Microcontroller User s Manual...

Страница 148: ...System Arbitration 8 24 lan SC520 Microcontroller User s Manual...

Страница 214: ...SDRAM Controller 10 36 lan SC520 Microcontroller User s Manual...

Страница 230: ...Write Buffer and Read Buffer 11 16 lan SC520 Microcontroller User s Manual...

Страница 288: ...GP Bus DMA Controller 14 22 lan SC520 Microcontroller User s Manual...

Страница 316: ...Programmable Interval Timer 16 8 lan SC520 Microcontroller User s Manual...

Страница 328: ...Software Timer 18 4 lan SC520 Microcontroller User s Manual...

Страница 346: ...Real Time Clock 20 12 lan SC520 Microcontroller User s Manual...

Страница 360: ...UART Serial Ports 21 14 lan SC520 Microcontroller User s Manual...

Страница 414: ...AMDebug Technology 26 8 lan SC520 Microcontroller User s Manual...