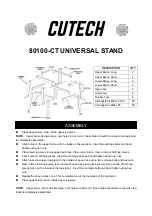

W632GU6NB

Publication Release Date: Aug. 20, 2018

Revision: A01

- 87 -

t

AOFmax

T0

T1

T2

T4

CK#

CK

DON'T CARE

T5

T3

ODT

T6

T7

T8

T9

T10

T11

VALID

TRANSITIONING

t

AOFmin

Address

Rtt_Nom

ODTH4

t

AONmin

t

AONmax

RTT

ODTLoff

VALID

VALID

VALID

VALID

VALID

VALID

VALID

VALID

VALID

VALID

VALID

Command

DQ

DQS, DQS#

ODTLon

Notes:

1. ODTH4 is defined from ODT registered high to ODT registered low, so in this example, ODTH4 is satisfied.

2. ODT registered low at T5 would also be legal.

Figure 78

– Dynamic ODT: Behavior without write command, AL = 0, CWL = 5

T0

T1

T2

T4

CK#

CK

DON'T CARE

T5

T3

ODT

T6

T7

T8

T9

T10

T11

NOP

TRANSITIONING

t

AOFmin

Address

Rtt_WR

t

AOFmax

ODTH8

t

AONmin

t

ADCmax

RTT

ODTLoff

WRS8

NOP

NOP

NOP

NOP

NOP

NOP

NOP

NOP

NOP

NOP

Command

DQ

DQS, DQS#

Din

b

Din

b+2

Din

b+3

Din

b+1

Din

b+5

Din

b+6

Din

b+4

Din

b+7

WL

ODTLcwn8

ODTLon

VALID

ODTLcnw

Note:

1. Example for BL8 (via MRS or OTF), AL = 0, CWL = 5. In this example, ODTH8 = 6 is exactly satisfied.

Figure 79

– Dynamic ODT: Behavior with ODT pin being asserted together with write command

for duration of 6 clock cycles