W632GU6NB

Publication Release Date: Aug. 20, 2018

Revision: A01

- 37 -

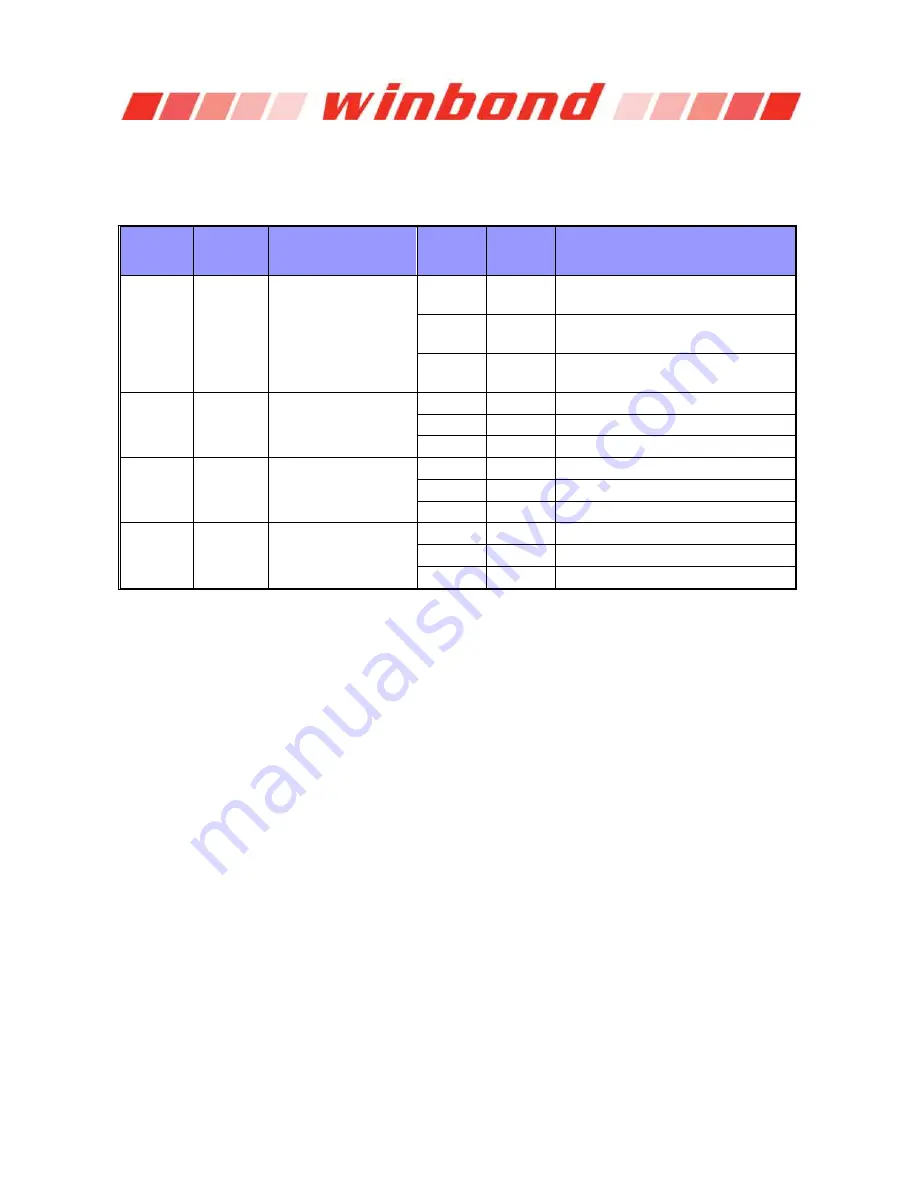

8.10.2 MPR Register Address Definition

Table 6 provides an overview of the available data locations, how they are addressed by MR3 A[1:0]

during a MRS to MR3, and how their individual bits are mapped into the burst order bits during a Multi

Purpose Register Read.

Table 6

– MPR Readouts and Burst Order Bit Mapping

MR3 A[2]

MR3 A[1:0]

Function

Burst

Length

Read

Address

A[2:0]

Burst Order and Data Pattern

1b

00b

Read Pre-defined Pattern

for System Calibration

BL8

000b

Burst order 0,1,2,3,4,5,6,7

Pre-defined Data Pattern [0,1,0,1,0,1,0,1]

BC4

000b

Burst order 0,1,2,3

Pre-defined Data Pattern [0,1,0,1]

BC4

100b

Burst order 4,5,6,7

Pre-defined Data Pattern [0,1,0,1]

1b

01b

RFU

BL8

000b

Burst order 0,1,2,3,4,5,6,7

BC4

000b

Burst order 0,1,2,3

BC4

100b

Burst order 4,5,6,7

1b

10b

RFU

BL8

000b

Burst order 0,1,2,3,4,5,6,7

BC4

000b

Burst order 0,1,2,3

BC4

100b

Burst order 4,5,6,7

1b

11b

RFU

BL8

000b

Burst order 0,1,2,3,4,5,6,7

BC4

000b

Burst order 0,1,2,3

BC4

100b

Burst order 4,5,6,7

Note:

Burst order bit 0 is assigned to LSB and the burst order bit 7 is assigned to MSB of the selected MPR agent.

8.10.3 Relevant Timing Parameters

The following AC timing parameters are important for operating the Multi Purpose Register: t

RP

, t

MRD

,

t

MOD

, and t

MPRR

. For more details refer to section 10.16

on page 139.

8.10.4 Protocol Example

Protocol Example (This is one example):

Read out pre-determined read-calibration pattern.

Description: Multiple reads from Multi Purpose Register, in order to do system level read timing

calibration based on pre-determined and standardized pattern.

Protocol Steps:

Precharge All.

Wait until t

RP

is satisfied.

Set MRS,

“MR3 A[2] = 1b” and “MR3 A[1:0] = 00b”.

This redirects all subsequent reads and load pre-defined pattern into Multi Purpose Register.

Wait until t

MRD

and t

MOD

are satisfied (Multi Purpose Register is then ready to be read). During the

period MR3 A[2] =1, no data write operation is allowed.