175

high.

F8.08

Sampling cycle T

0.01

~

100.00s

0.10

0.00

:

automatic

Sampling cycle corresponds to feedback. Regulator operates once in every sampling cycle. The longer of the cycle, the

slower of the response, but the better of the suppress effect to interference signal. Normally no need to set this

parameter.

F8.09

Error limit

0.0

~

100.0

%

0.0%

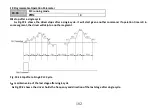

Error limit is the ratio of deviation (feedback and reference) absolute value to reference. PID regulator stops operation

when feedback is within this range, as showed in the following figure. Setting this parameter correctly is helpful to

improve the system stability, as frequent adjustment around target value can be avoided.

Fig. F8-3 Error Limit Schematic Diagram