CDJ-800MK2

40

1

2

3

4

1

2

3

4

C

D

F

A

B

E

28

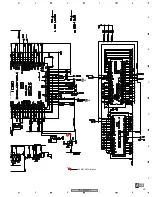

CH1 : SRV16M

from FPGA

V: 5.0 V/div. H: 200 msec/div.

20

CH2 : SRVRST

from CPU

V: 5.0 V/div. H: 200 msec/div.

36

CH3 : SRVBUS0

CPU - SRV

V: 5.0 V/div. H: 200 msec/div.

37

CH4 : DRVMUTE1

from CPU to IC102

V: 5.0 V/div. H: 200 msec/div.

Configuration (1/2)

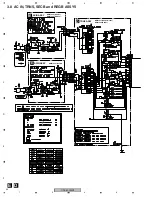

29

CH1 : DSP16M

from FPGA

V: 5.0 V/div. H: 200 msec/div.

21

CH2 : DSPRST

from CPU

V: 5.0 V/div. H: 200 msec/div.

31

CH3 : DSPSIN

to CPU

V: 5.0 V/div. H: 200 msec/div.

32

CH4 : CLK

from CPU

V: 5.0 V/div. H: 200 msec/div.

Configuration (1/2)

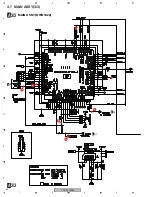

22

CH1 : V+3D

V: 2.0 V/div. H: 10 msec/div.

18

CH2 : RST

from Reset IC to CPU

V: 2.0 V/div. H: 10 msec/div.

Delay time of Reset IC (IC304)

22

CH1 : V+3D

V: 5.0 V/div. H: 10 msec/div.

71

CH2 : CPU16M

from IC310 to CPU

V: 5.0 V/div. H: 10 msec/div.

18

CH3 : RST

from Reset IC to CPU

V: 5.0 V/div. H: 10 msec/div.

Association between the 16.93 MHz clock

signal and resetting of the MPU

23

CH1 : PROG_B (IC302 - pin 99)

from CPU to FPGA

V: 5.0 V/div. H: 100 msec/div.

24

CH2 : XINIT

to CPU

V: 5.0 V/div. H: 100 msec/div.

25

CH3 : CLK

from CPU to FPGA

V: 5.0 V/div. H: 100 msec/div.

26

CH4 : DATA

from CPU

V: 5.0 V/div. H: 100 msec/div.

Configuration (1/3)

MPU

MPU

Servo DSP

FPGA

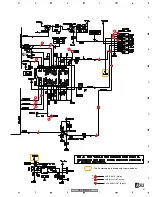

24

CH2 : XINIT

to CPU

V: 5.0 V/div. H: 100 msec/div.

26

CH4 : DATA

from CPU

V: 5.0 V/div. H: 100 msec/div.

27

CH5 : DONE

to CPU

V: 5.0 V/div. H: 100 msec/div.

30

CH8 : XFRST

from CPU

V: 5.0 V/div. H: 100 msec/div.

Configuration (2/3)

FPGA

27

CH5 : DONE

to CPU

V: 5.0 V/div. H: 100 msec/div.

28

CH6 : SRV16M

to IC101

V: 5.0 V/div. H: 100 msec/div.

29

CH7 : DSP16M

to IC701

V: 5.0 V/div. H: 100 msec/div.

30

CH8 : XFRST

from CPU

V: 5.0 V/div. H: 100 msec/div.

Configuration (3/3)

FPGA

Audio DSP

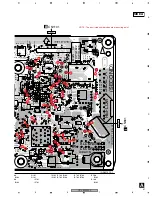

MAIN ASSY

A

Conditions:

At the time of power on, without a disc loaded

Remark:

Set value for reset delay time: 70 msec

Conditions:

At the time of power on, without a disc loaded

Conditions:

At the time of power on, without a disc loaded

Conditions:

At the time of power on, without a disc loaded

Conditions:

At the time of power on, without a disc loaded

Conditions:

At the time of power on, without a disc loaded

29

CH1 : DSP16M

from FPGA

V: 5.0 V/div. H: 200 msec/div.

26

CH5 : DATA

from CPU

V: 5.0 V/div. H: 200 msec/div.

34

CH6 : DSPDREQ

to FPGA & CPU

V: 5.0 V/div. H: 200 msec/div.

35

CH7 : DAC11M

to IC702

V: 5.0 V/div. H: 200 msec/div.

Configuration (2/2)

Audio DSP

Conditions:

At the time of power on, without a disc loaded

Conditions:

At the time of power on, without a disc loaded

28

CH1 : SRV16M

from FPGA

V: 5.0 V/div. H: 200 msec/div.

20

CH2 : SRVRST

from CPU

V: 5.0 V/div. H: 200 msec/div.

36

CH3 : SRVBUS0

CPU - SRV

V: 5.0 V/div. H: 200 msec/div.

38

CH5 : DRVMUTE2

from CPU to IC102

V: 5.0 V/div. H: 200 msec/div.

Configuration (2/2)

Servo DSP

Conditions:

At the time of power on, without a disc loaded

CH1

CH2

CH1

CH5

CH6

CH7

CH1

CH2

CH3

CH4

CH1

CH2

CH3

CH5

CH4

CH5

CH5

CH6

CH7

CH8

CH1

CH2

CH3

CH4

CH8

CH2

CH1

CH1

CH2

CH3

CH4

CH2

CH3

Power ON

Reset clear

a - b : 68.7 msec

a - b : 442 msec

a - c : 682 msec

a - b : 670 msec

a - b : 67.8 msec

a - b : 681 msec

a - b : 1 256 msec

a - b : 680 msec

a - b : 1 256 msec

a - c : 1 318 msec

a - b : 69 msec

a - c : 442 msec

b - c : 373 msec

3.3 V

a

a

a

a

a

b

b

c

b

c

b

b

b

a

a

b

a

b

b

a

c

3.3 V

Summary of Contents for CDJ-800MK2

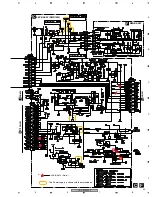

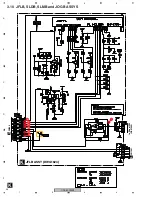

Page 27: ...CDJ 800MK2 27 5 6 7 8 5 6 7 8 C D F A B E MODE MODE 3 3 A 27 24 26 19 36 ...

Page 29: ...CDJ 800MK2 29 5 6 7 8 5 6 7 8 C D F A B E Data PANEL DATA Digital A 2 3 3 3 A 3 3 A 23 ...

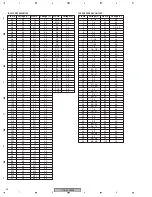

Page 130: ...CDJ 800MK2 130 1 2 3 4 1 2 3 4 C D F A B E Pin Function ...

Page 135: ...CDJ 800MK2 135 5 6 7 8 5 6 7 8 C D F A B E Pin Function ...

Page 139: ...CDJ 800MK2 139 5 6 7 8 5 6 7 8 C D F A B E Pin Function ...

Page 143: ...CDJ 800MK2 143 5 6 7 8 5 6 7 8 C D F A B E ...

Page 153: ...CDJ 800 7 5 6 7 8 5 6 7 8 C D F A B E ...