CDJ-800MK2

93

5

6

7

8

5

6

7

8

C

D

F

A

B

E

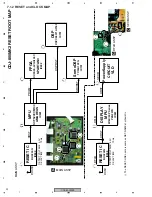

MAIN ASSY

.TC7WU04FU

CPU16M

70MHz

CLK

VSS1084-A

FP16M

DSP16M

DAC11M

DFLB

DFLB

FLSCLK

TSCLK

TSCLK

SRV16M

JFLB

JSCLK

.DSS1149-A

: Discontinuous Clock Line

: The current of line is possible to drive variable.

The CLOCK-LINE name is same as NET-NAME of schematic.

MPU

SCF5249VM140

AMADEUS

IC301

DSP

DSPC56371AF180

IC701

FPGA

XC3S50 Series

SPARTAN-3

IC302

ServoDSP

TC94A15FG

IC101

DISPLAY

MPU

M16C/30P Series

PEG237B

IC501

DAC

PE8001A

IC702

11MHz

16MHz

16MHz

16.9344MHz

16.000MHz

SDRAM

K4S641632K-UC75

HY57V641620ETP-H

70MHz

X'TAL

FUNDAMENTAL

Tolerance

±

50ppm

Temp. Drift

±

50ppm

X'TAL

FUNDAMENTAL

Tolerance

±

20ppm

Temp. Drift

±

30ppm

DATA-FL

DEL1059-x

JOG-FL

DEL1058-x

1.6MHz

400kHz

1MHz

CDJ-800MK2 CLOCk DELIVERY MAP

Output current adjustment is possible

instead of the buffer by way of the FPGA

inside, and suppress the return-loss by

outputting a clock from different port.

70MHz and 16MHz do not

interfere in the FPGA inside.

(Other block)

Output a clock only in the

display data

transmission.

X'TAL

X'TAL

B

DFLB ASSY

MAIN ASSY

A

A

B

G

A

Summary of Contents for CDJ-800MK2

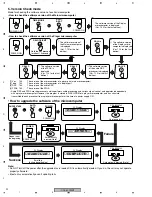

Page 27: ...CDJ 800MK2 27 5 6 7 8 5 6 7 8 C D F A B E MODE MODE 3 3 A 27 24 26 19 36 ...

Page 29: ...CDJ 800MK2 29 5 6 7 8 5 6 7 8 C D F A B E Data PANEL DATA Digital A 2 3 3 3 A 3 3 A 23 ...

Page 130: ...CDJ 800MK2 130 1 2 3 4 1 2 3 4 C D F A B E Pin Function ...

Page 135: ...CDJ 800MK2 135 5 6 7 8 5 6 7 8 C D F A B E Pin Function ...

Page 139: ...CDJ 800MK2 139 5 6 7 8 5 6 7 8 C D F A B E Pin Function ...

Page 143: ...CDJ 800MK2 143 5 6 7 8 5 6 7 8 C D F A B E ...

Page 153: ...CDJ 800 7 5 6 7 8 5 6 7 8 C D F A B E ...