CDJ-800MK2

117

5

6

7

8

5

6

7

8

C

D

F

A

B

E

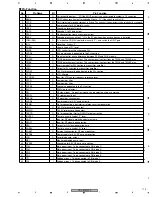

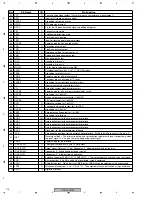

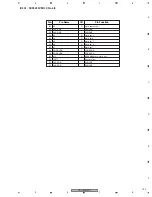

A15 1

A16

48

A14 2

BYTE

47

A13 3

VSS

46

A12 4

DQ15/A-1

45

A11 5

DQ7

44

A10 6

DQ14

43

A9 7

DQ6

42

A8 8

DQ13

41

N.C. 9

DQ5

40

N.C. 10

DQ12

39

WE 11

DQ4

38

RESET 12

VCC

37

N.C. 13

DQ11

36

N.C. 14

DQ3

35

RY/BY 15

DQ10

34

A18 16

DQ2

33

A17 17

DQ9

32

A7 18

DQ1

31

A6 19

DQ8

30

A5 20

DQ0

29

A4 21

OE

28

A3 22

VSS

27

A2 23

CE

26

A1 24

A0

25

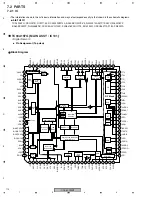

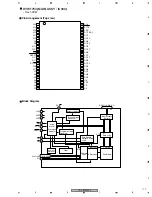

DYW1753 (MAIN ASSY : IC300)

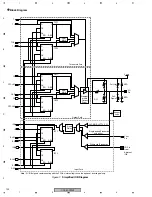

• Flash ROM

Block Diagram

Pin Arrangement (Top view)

VCC

Selector Switch

RY/BY

Program Voltage

Generator

Timer

Low Vcc

Detector

Chip Enable

Output Enable

Logic

Erase Voltage

Generator

Input/Output

Buffers

Data Latch

Y-Gating

Cell Matrix

State

Control

Command

Register

DQ15 to DQ0 (A-1)

37

37

VSS

27

VSS

46

WE

11

BYTE

47

RESET

12

CE

26

OE

28

A-1

A18 to A0

45

Y-Decoder

STB

STB

X-Decoder

Address

Latch

1-8,16-25,48

29-36,38-45

Summary of Contents for CDJ-800MK2

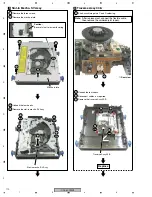

Page 27: ...CDJ 800MK2 27 5 6 7 8 5 6 7 8 C D F A B E MODE MODE 3 3 A 27 24 26 19 36 ...

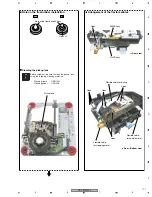

Page 29: ...CDJ 800MK2 29 5 6 7 8 5 6 7 8 C D F A B E Data PANEL DATA Digital A 2 3 3 3 A 3 3 A 23 ...

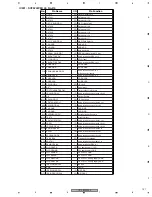

Page 130: ...CDJ 800MK2 130 1 2 3 4 1 2 3 4 C D F A B E Pin Function ...

Page 135: ...CDJ 800MK2 135 5 6 7 8 5 6 7 8 C D F A B E Pin Function ...

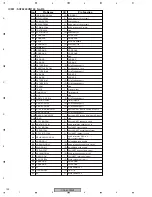

Page 139: ...CDJ 800MK2 139 5 6 7 8 5 6 7 8 C D F A B E Pin Function ...

Page 143: ...CDJ 800MK2 143 5 6 7 8 5 6 7 8 C D F A B E ...

Page 153: ...CDJ 800 7 5 6 7 8 5 6 7 8 C D F A B E ...