CDJ-800MK2

132

1

2

3

4

1

2

3

4

C

D

F

A

B

E

Figure 1:

Simplified IOB Diagram

D

CE

CK

TFF1

Three-state Path

T

T1

TCE

T2

TFF2

Q

SR

DDR

MUX

REV

D

CE

CK

Q

SR

REV

D

CE

CK

OFF1

Output Path

O1

OCE

O2

OFF2

Q

SR

DDR

MUX

Keeper

Latch

V

CCO

V

REF

Pin

I/O Pin

from

Adjacent

IOB

I/O

Pin

Program-

mable

Output

Driver

DCI

ESD

Pull-Up

Pull-

Down

ESD

REV

D

CE

CK

Q

SR

REV

OTCLK1

OTCLK2

D

CE

CK

IFF1

Input Path

I

ICE

IFF2

Q

SR

Fixed

Delay

LVCMOS, LVTTL, PCI

Single-ended Standards

using V

REF

Differential Standards

REV

D

CE

CK

Q

SR

REV

ICLK1

ICLK2

SR

REV

Note : All IOB signals communicating with the FPGA's internal logic have the option of inverting polarity.

IQ1

IQ2

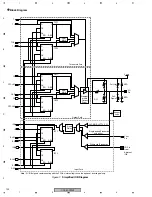

Block Diagram

Summary of Contents for CDJ-800MK2

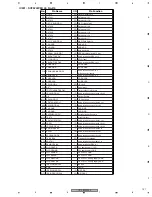

Page 27: ...CDJ 800MK2 27 5 6 7 8 5 6 7 8 C D F A B E MODE MODE 3 3 A 27 24 26 19 36 ...

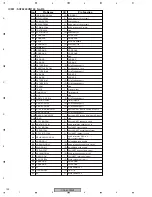

Page 29: ...CDJ 800MK2 29 5 6 7 8 5 6 7 8 C D F A B E Data PANEL DATA Digital A 2 3 3 3 A 3 3 A 23 ...

Page 130: ...CDJ 800MK2 130 1 2 3 4 1 2 3 4 C D F A B E Pin Function ...

Page 135: ...CDJ 800MK2 135 5 6 7 8 5 6 7 8 C D F A B E Pin Function ...

Page 139: ...CDJ 800MK2 139 5 6 7 8 5 6 7 8 C D F A B E Pin Function ...

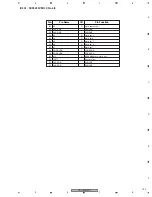

Page 143: ...CDJ 800MK2 143 5 6 7 8 5 6 7 8 C D F A B E ...

Page 153: ...CDJ 800 7 5 6 7 8 5 6 7 8 C D F A B E ...