CDJ-800

16

1

2

3

4

1

2

3

4

C

D

F

A

B

E

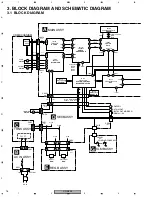

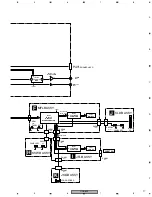

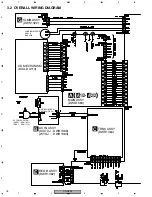

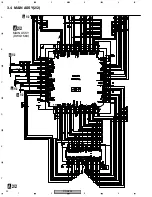

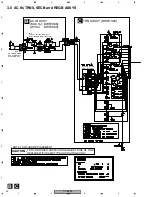

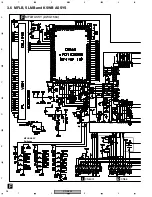

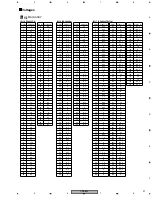

3. BLOCK DIAGRAM AND SCHEMATIC DIAGRAM

3.1 BLOCK DIAGRAM

IC118

TA2153FN

RF AMP

IC119

LA6562

BTL DRIVER

IC110

TC9495F

SERVO

PROCESSOR

IC102

PDC101A

ASIC

IC109

K4S281632C-TC1H

SDRAM

IC112

PD3442B8

SYSTEM CONTROL

MICROCOMPUTER

IC117

XCA56367PV150

DSP

48

49

25

14

17

38

46

43

18

19

FOO

A-F

T+,T-

F+,F-

T+,T-

F+,F-

A-F

SL+

SL-

SP-

SP+

LO-

LO+

TRO

RFO

8

83

AOUT

50MHz

5

85

LRCK

7

84

88

67

60

11

55

4

27

BCK

16MHz

25MHz

O_SDATA

TEO

FEO

RFI

25MHz

25MHz

25MHz

SDOO

ADO

TEI

FEI

A

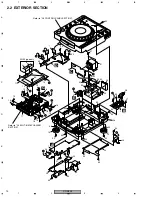

MAIN ASSY

CD MECHANISM

CN113

(16P)

CN111

(6P)

PICKUP

ASSY

SPINDLE

MOTOR

SLED

MOTOR

+

–

M

LO-

LO+

V+7B

LOADING

MOTOR

+

–

M

+

–

M

4

7

9

14

1

4

11

14

3

CN122

(25P)

CN56

(19P)

CN53

(25P)

CN51

(11P)

CN22

(11P)

CN11

T21 PT

CN52

(6P)

LOADING PHASE SW

J91

(6P)

CN54

2

1

24

1

1

2

1

2

3

1

3

25

6

4

2

1

11

9

11

9

7

2

8

V+11B

1

9

4

78

16MHz

28

61

5

IC113

BR24C64F

EEPROM

IC122

M51957BFP

RESET IC

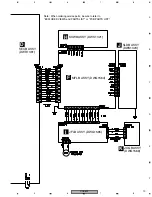

G

SLMB ASSY

E

REGB ASSY

D

SECB ASSY

C

TRNS ASSY

B

AC IN ASSY

CN55

(3P)

CONTROL

DATA IN/OUT

DIGITAL OUT MODE SW

NORMAL

—

DJ

CN1901

(3P)

V+5D

V+7A

V+11B

V+7B

IC91

BA05T

REG.

4

5

4

5

IC92

PQ15RW11

REG.

AC IN

AN11

LIVE

NEUTRAL

LR Clock Audio

BCK

Data

Parallel data

BUS0

BUS1

BUS2

BUS3

Serial data in

data out

Clock

Enable

Summary of Contents for CDJ-800MK2

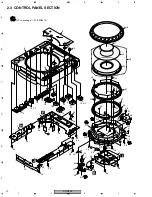

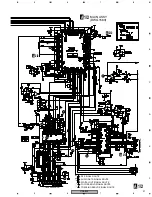

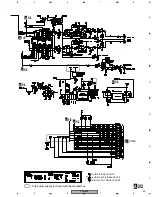

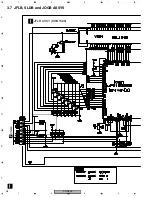

Page 27: ...CDJ 800MK2 27 5 6 7 8 5 6 7 8 C D F A B E MODE MODE 3 3 A 27 24 26 19 36 ...

Page 29: ...CDJ 800MK2 29 5 6 7 8 5 6 7 8 C D F A B E Data PANEL DATA Digital A 2 3 3 3 A 3 3 A 23 ...

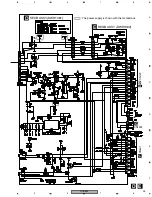

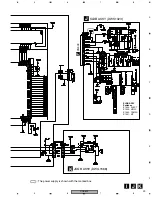

Page 130: ...CDJ 800MK2 130 1 2 3 4 1 2 3 4 C D F A B E Pin Function ...

Page 135: ...CDJ 800MK2 135 5 6 7 8 5 6 7 8 C D F A B E Pin Function ...

Page 139: ...CDJ 800MK2 139 5 6 7 8 5 6 7 8 C D F A B E Pin Function ...

Page 143: ...CDJ 800MK2 143 5 6 7 8 5 6 7 8 C D F A B E ...

Page 153: ...CDJ 800 7 5 6 7 8 5 6 7 8 C D F A B E ...