CDJ-800MK2

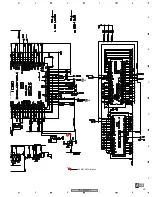

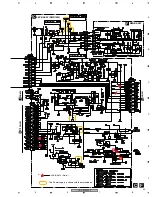

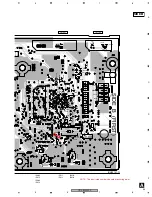

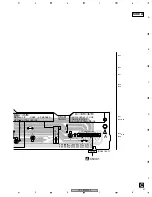

43

5

6

7

8

5

6

7

8

C

D

F

A

B

E

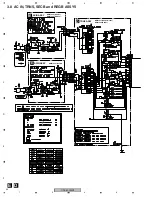

48

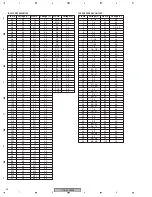

CH1 : V+5

V: 2.0 V/div. H: 10 msec/div.

49

CH2 : XRST

to DISP_CPU

V: 2.0 V/div. H: 10 msec/div.

Delay time of Reset IC (IC502)

DISPLAY_MPU

DATA-FL

DISPLAY_MPU

DATA-FL

DISPLAY_MPU

DATA-FL

Conditions

: At the time of power on, without a disc loaded

Remark:

Set value for reset delay time: 70 msec

Conditions:

At the time of power on, without a disc loaded

54

CH1 : FLBK

V: 5.0 V/div. H: 100 msec/div.

55

CH2 : FLLAT

V: 5.0 V/div. H: 100 msec/div.

56

CH3 : FLSDO

V: 5.0 V/div. H: 100 msec/div.

57

CH4 : FLSCLK

V: 5.0 V/div. H: 100 msec/div.

Three-wire serial lines (at the time of power on)

Conditions:

At the time of power on, without a disc loaded

48

CH1 : V+5

V: 5.0 V/div. H: 10 msec/div.

72

CH2 : XOUT

to DISP_CPU

V: 5.0 V/div. H: 10 msec/div.

49

CH3 : XRST

to DISP_CPU

V: 5.0 V/div. H: 10 msec/div.

Association between 16 MHz clock signal and

resetting of the DISPLAY_MPU

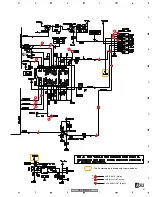

73

CH5 : VLDD

V: 20.0 V/div. H: 100 msec/div.

48

CH6 : 5V

V: 5.0 V/div. H: 100 msec/div.

54

CH1 : FLBK

V: 5.0 V/div. H: 100 msec/div.

74

CH7 : FLAC1 and FLAC2

V: 5.0 V/div. H: 100 msec/div.

Association between the built-in driver and

the VLDD power

Conditions:

At the time of power on, without a disc loaded

Remark:

According to the FL specifications, the Vload

power must be stably supplied before the built-in

driver starts.

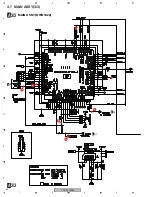

50

CH1 : TSCLK

V: 5.0 V/div. H: 200 msec/div.

51

CH2 : TSCS

V: 5.0 V/div. H: 200 msec/div.

52

CH3 : TSDI

V: 5.0 V/div. H: 200 msec/div.

53

CH4 : TSDO

V: 5.0 V/div. H: 200 msec/div.

Communication between the FPGA and

DISPLAY_MPU (3-wire serial)

Conditions:

At the time of power on,

without a disc loaded

54

CH1 : FLBK

V: 5.0 V/div. H: 1 msec/div.

55

CH2 : FLLAT

V: 5.0 V/div. H: 1 msec/div.

56

CH3 : FLSDO

V: 5.0 V/div. H: 1 msec/div.

57

CH4 : FLSCLK

V: 5.0 V/div. H: 1 msec/div.

Three-wire serial lines

(during indication on the FL display)

Conditions:

During playback

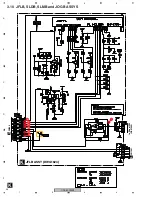

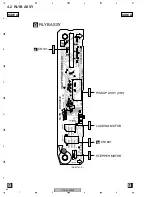

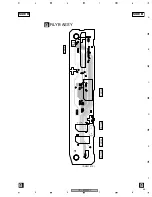

DFLB ASSY

G

SLDB ASSY

J

Tempo slider

68

CH1 : ADIN

Detect DATA

V: 1.0 V/div. H: 500 msec/div.

67

CH2 : ADCT

Compare Level

V: 1.0 V/div. H: 500 msec/div.

69

CH3 : GNDAD

GND Level

V: 1.0 V/div. H: 500 msec/div.

Slide operation

Conditions:

When the slider is moved from –100% to +100%

CH1

CH1

CH2

CH3

CH1

CH2

CH3

CH4

CH5

CH6

CH1

CH1

CH2

CH3

CH4

CH7

CH1

CH1

CH2

CH3

CH4

CH2

CH3

CH2

Power ON

Reset clear

Power ON

TEMPO -100% point

(MP3 -16%)

TEMPO +100% point

(MP3 +16%)

TEMPO 0% point

5.0 V

Power ON

Power ON

a

b

a

c

b

d

a - b : 70.10 msec

Expansion B

2.5 V

Expansion A

Expansion C

Expansion D

a - b : 169.5 msec

a - c : 679.7 msec

a - d : 1 186.4 msec

Summary of Contents for CDJ-800MK2

Page 27: ...CDJ 800MK2 27 5 6 7 8 5 6 7 8 C D F A B E MODE MODE 3 3 A 27 24 26 19 36 ...

Page 29: ...CDJ 800MK2 29 5 6 7 8 5 6 7 8 C D F A B E Data PANEL DATA Digital A 2 3 3 3 A 3 3 A 23 ...

Page 130: ...CDJ 800MK2 130 1 2 3 4 1 2 3 4 C D F A B E Pin Function ...

Page 135: ...CDJ 800MK2 135 5 6 7 8 5 6 7 8 C D F A B E Pin Function ...

Page 139: ...CDJ 800MK2 139 5 6 7 8 5 6 7 8 C D F A B E Pin Function ...

Page 143: ...CDJ 800MK2 143 5 6 7 8 5 6 7 8 C D F A B E ...

Page 153: ...CDJ 800 7 5 6 7 8 5 6 7 8 C D F A B E ...