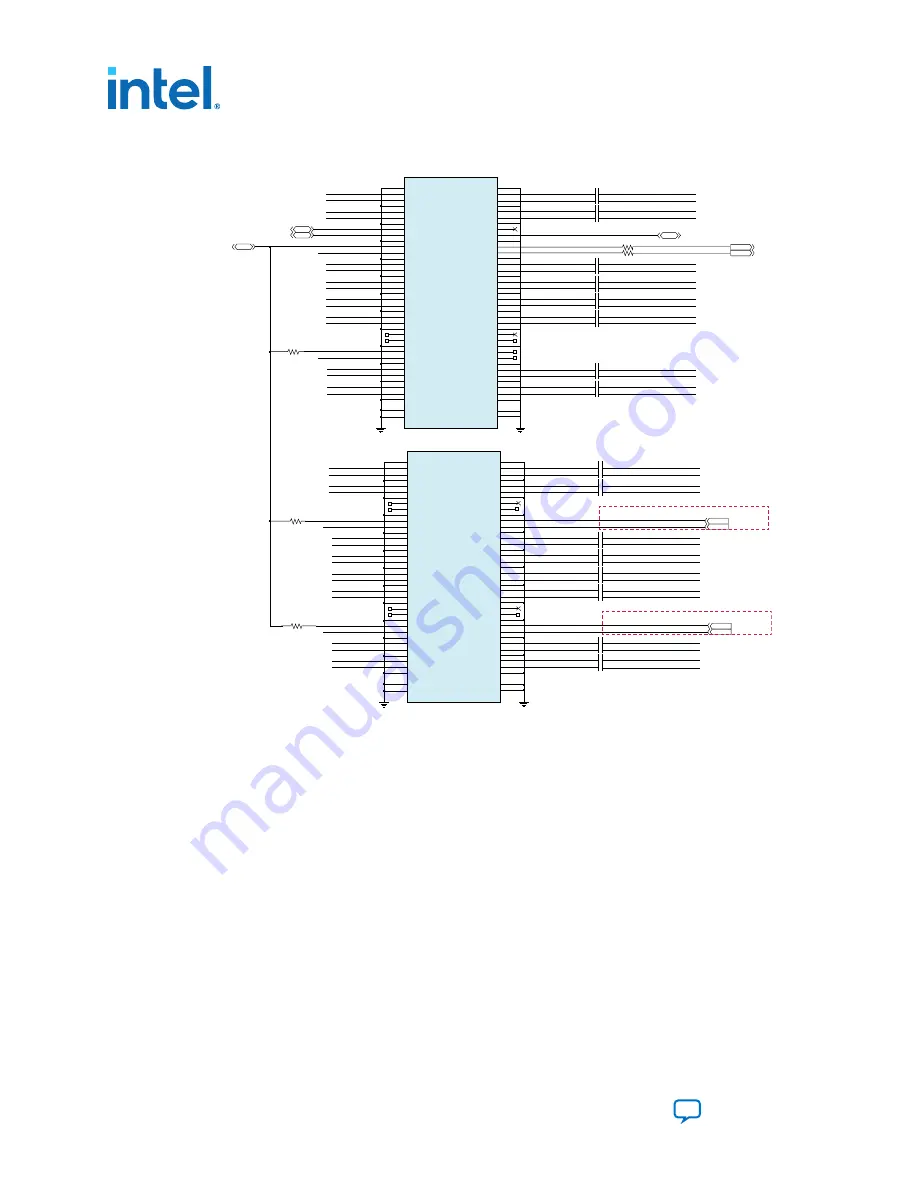

Figure 31.

MCIO Connector Circuit

J6

GND_A1

CXL_RX_P0

CXL_RX_N0

CXL_RX_P1

CXL_RX_N1

CXL_PRSNTx1_N

CXL_RX_P2

CXL_RX_P3

CXL_RX_N2

CXL_RX_N3

CXL_RX_P4

CXL_RX_N4

CXL_RX_P5

CXL_RX_P6

CXL_RX_N5

CXL_RX_N6

CXL_RX_P7

CXL_RX_N7

CXL_PERST1_N

CXL_PRSNTx4_N

0, DNI

R187

I2C2_SCL 27, 46, 50, 52

I2C2_SDA 27, 46, 50, 52

CXL_PERSTn 33, 48, 52

RX0_0P

RX0_0N

GND_A4

RX0_1P

RX0_1N

GND_A7

SMB0_SCL

SMB0_SDA

GND_A10

PERST0_N

PRSNT0_N

GND_A13

RX0_2P

RX0_2N

GND_A16

RX0_3P

RX0_3N

GND_A19

RX1_0P

RX1_0N

GND_A22

RX1_1P

RX1_1N

GND_A25

SMB1_SCL

SMB1_SDA

GND_A28

PERST1_N

PRSNT1_N

GND_A31

RX1_2P

RX1_2N

GND_A34

RX1_3P

RX1_3N

GND_A37

MH1

MH3

GND_B1

CXL_TX_C_P0

C354

0.22uF SMC0201IA

CXL_TX_P0

0.22uF SMC0201IA

49 CXL_SMB_ALERT_N

CXL_TX_N1

0.22uF SMC0201IA

CXL_TX_P1

0.22uF SMC0201IA

CXL_TX_N0

CXL_TX_C_N0

C355

CXL_TX_C_P1

C356

CXL_TX_C_N1

CLK_100M_CXL_CONN_C_P

R185

0

45 CLK_CXL_CONN_P

CLK_100M_CXL_CONN_C_N

R186

0

45 CLK_CXL_CONN_N

C357

0.22uF SMC0201IA

CXL_TX_P2

CXL_TX_C_P2

C358

0.22uF SMC0201IA

CXL_TX_P3

CXL_TX_C_P3

C360

0.22uF SMC0201IA

CXL_TX_N3

CXL_TX_C_P3

C361

0.22uF SMC0201IA

CXL_TX_P4

CXL_TX_C_P4

C362

0.22uF SMC0201IA

CXL_TX_N4

CXL_TX_C_N4

C363

0.22uF SMC0201IA

CXL_TX_P5

CXL_TX_C_P5

C364

0.22uF SMC0201IA

CXL_TX_N5

CXL_TX_C_N5

C365

0.22uF SMC0201IA

CXL_TX_P6

CXL_TX_C_P6

C366

0.22uF SMC0201IA

CXL_TX_N6

CXL_TX_C_N6

C367

0.22uF SMC0201IA

CXL_TX_P7

CXL_TX_C_P7

C368

0.22uF SMC0201IA

CXL_TX_N7

CXL_TX_C_N7

C369

0.22uF SMC0201IA

CXL_TX_N2

CXL_TX_C_N2

C359

TX0_0P

TX0_0N

GND_B4

TX0_1P

TX0_1N

GND_B7

NC_B8

SMB0_ALERT_N

GND_B10

CLK0_DP

CLK0_DN

GND_B13

TX0_2P

TX0_2N

GND_B16

TX0_3P

TX0_3N

GND_B19

TX1_0P

TX1_0N

GND_B22

TX1_1P

TX1_1N

GND_B25

NC_B26

SMB1_ALERT_N

GND_B28

CLK1_DP

CLK1_DN

GND_B31

TX1_2P

TX1_2N

GND_B34

TX1_3P

TX1_3N

GND_B37

MH2

MH4

MCIO_74P_G97V22312HR

K64129-002

J7

GND_A1

RX0_0P

RX0_0N

GND_A4

RX0_1P

RX0_1N

GND_A7

SMB0_SCL

SMB0_SDA

GND_A10

PERST0_N

PRSNT0_N

GND_A13

RX0_2P

RX0_2N

GND_A16

RX0_3P

RX0_3N

GND_A19

RX1_0P

RX1_0N

GND_A22

RX1_1P

RX1_1N

GND_A25

SMB1_SCL

SMB1_SDA

GND_A28

PERST1_N

PRSNT1_N

GND_A31

RX1_2P

RX1_2N

GND_A34

RX1_3P

RX1_3N

GND_A37

MH1

MH3

GND_B1

TX0_0P

TX0_0N

GND_B4

TX0_1P

TX0_1N

GND_B7

NC_B8

SMB0_ALERT_N

GND_B10

CLK0_DP

CLK0_DN

GND_B13

TX0_2P

TX0_2N

GND_B16

TX0_3P

TX0_3N

GND_B19

TX1_0P

TX1_0N

GND_B22

TX1_1P

TX1_1N

GND_B25

NC_B26

SMB1_ALERT_N

GND_B28

CLK1_DP

CLK1_DN

GND_B31

TX1_2P

TX1_2N

GND_B34

TX1_3P

TX1_3N

GND_B37

MH2

MH4

MCIO_74P_G97V22312HR

K64129-002

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

A36

A37

MH1

MH3

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

B36

B37

MH2

MH4

CXL_RX_P8

CXL_RX_N8

CXL_RX_P9

CXL_RX_N9

CXL_PRSNTx8_N

CXL_PERST2_N

CXL_RX_P10

CXL_RX_P11

CXL_RX_N10

CXL_RX_N11

CXL_RX_P12

CXL_RX_N12

CXL_RX_P13

CXL_RX_P14

CXL_RX_N13

CXL_RX_N14

CXL_RX_P15

CXL_RX_N15

CXL_PERST3_N

CXL_PRSNTx16_N

0, DNI

R189

R188

0, DNI

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

A36

A37

MH1

MH3

CXL_TX_C_P8

C373

0.22uF SMC0201IA

CXL_TX_P8

0.22uF SMC0201IA

CXL_TX_N9

Design Note:

Clock for RootPort mode.

0.22uF SMC0201IA

CXL_TX_P9

0.22uF SMC0201IA

CXL_TX_N8

CXL_TX_C_N8

C374

CXL_TX_C_P9

C375

CXL_TX_C_N9

44 REFCLK_CXL_RP_P1

44 REFCLK_CXL_RP_N1

C376

0.22uF SMC0201IA

CXL_TX_P10

CXL_TX_C_P10

C377

0.22uF SMC0201IA

CXL_TX_P11

CXL_TX_C_P11

C379

0.22uF SMC0201IA

CXL_TX_N11

CXL_TX_C_P11

C380

0.22uF SMC0201IA

CXL_TX_P12

CXL_TX_C_P12

C381

0.22uF SMC0201IA

CXL_TX_N12

CXL_TX_C_N12

C382

0.22uF SMC0201IA

CXL_TX_P13

CXL_TX_C_P13

C383

0.22uF SMC0201IA

CXL_TX_N13

CXL_TX_C_N13

C384

0.22uF SMC0201IA

CXL_TX_P14

CXL_TX_C_P6

C385

0.22uF SMC0201IA

CXL_TX_N14

CXL_TX_C_N6

C386

0.22uF SMC0201IA

CXL_TX_P15

CXL_TX_C_P7

C387

0.22uF SMC0201IA

CXL_TX_N15

CXL_TX_C_N7

C388

0.22uF SMC0201IA

CXL_TX_N10

CXL_TX_C_N10

C378

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

B36

B37

MH2

MH4

Design Note:

Clock for RootPort mode.

44 REFCLK_CXL_RP_P0

44 REFCLK_CXL_RP_N0

A.5. MCIO Cable Assembly Information

The cable is not provided with the development kit. For more information, contact

Intel Premier Support and quote ID #14016163317.

A.6. Network Interfaces

The development kit supports two QSFPDD connectors each, connecting to the Intel

Agilex's F-tile (12A) transceivers. Each port can operate at 4x 58G or 8x 28G. These

two ports support ZQSFP56 SR optical modules as well as the 3M DAC electrical

cables. A Texas Instruments FPC202 dual-port controller serves as the low-speed

signal aggregator that makes up the Dual 100Gpbs Ethernet interfaces. The FPC202

aggregates all low speed and I2C signals across two ports and presents it as a single

management interface to the host.

A. Development Kits Components

683288 | 2022.09.22

Intel

®

Agilex

™

I-Series FPGA Development Kit User Guide

44