Rev. 1.0, 09/01, page 63 of 904

Section 4 Exception Handling

4.1

Exception Handling Types and Priority

As table 4.1 indicates, exception handling may be caused by a reset, trace, interrupt, or trap

instruction. Exception handling is prioritized as shown in table 4.1. If two or more exceptions

occur simultaneously, they are accepted and processed in order of priority. Exception sources, the

stack structure, and operation of the CPU vary depending on the interrupt control mode. For

details on the interrupt control mode, refer to section 5, Interrupt Controller.

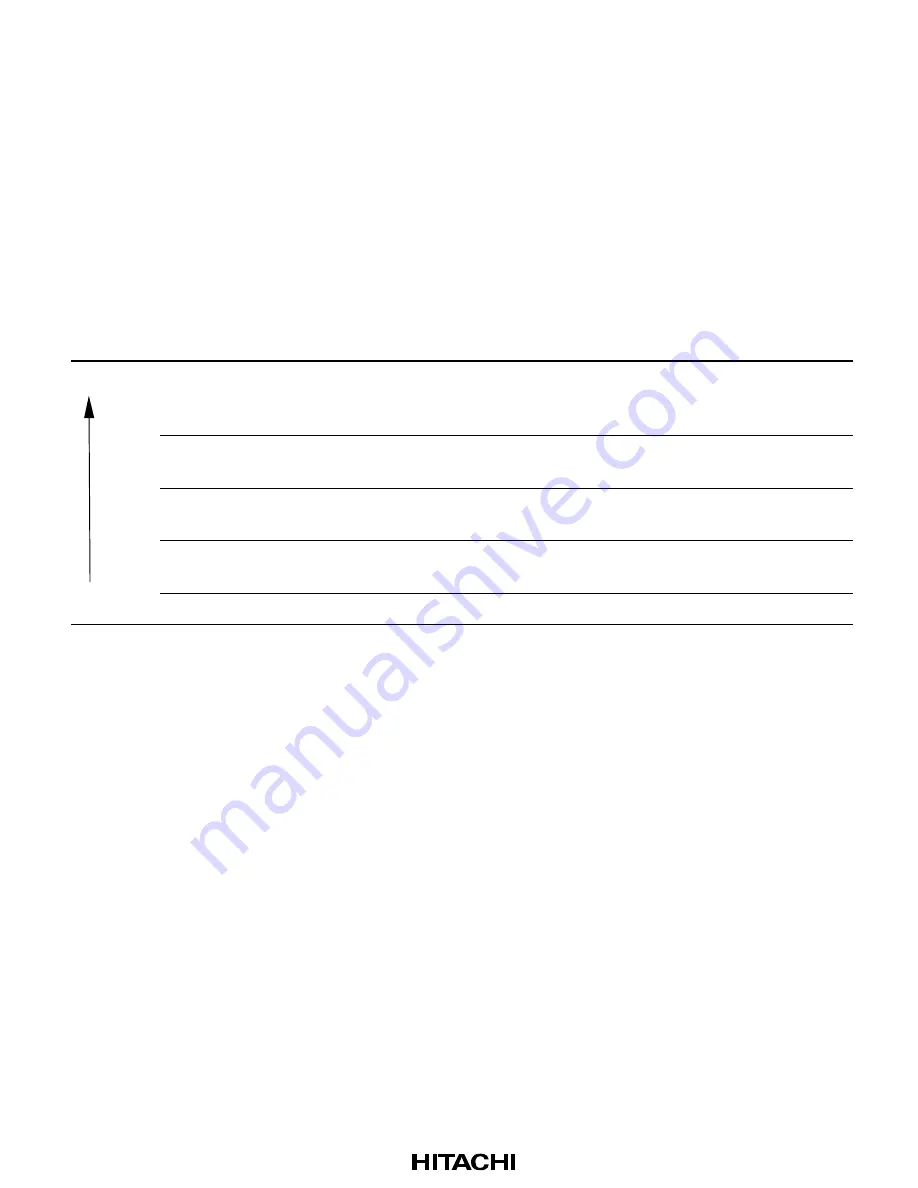

Table 4.1

Exception Types and Priority

Priority

Exception Type

Start of Exception Handling

High

Reset

Starts immediately after a low-to-high transition at the

5(6

pin, or when the watchdog timer overflows. The CPU enters

the reset state when the

5(6

pin is low.

Trace

*

1

Starts when execution of the current instruction or exception

handling ends, if the trace (T) bit in the EXR is set to 1.

Direct transition

*

2

Starts when the direct transition occurs by execution of the

SLEEP instruction.

Interrupt

Starts when execution of the current instruction or exception

handling ends, if an interrupt request has been issued.

*

3

Low

Trap instruction

*

4

Started by execution of a trap instruction (TRAPA)

Notes: 1. Traces are enabled only in interrupt control mode 2. Trace exception handling is not

executed after execution of an RTE instruction.

2. Not available in this LSI.

3. Interrupt detection is not performed on completion of ANDC, ORC, XORC, or LDC

instruction execution, or on completion of reset exception handling.

4. Trap instruction exception handling requests are accepted at all times in program

execution state.

4.2

Exception Sources and Exception Vector Table

Different vector addresses are assigned to different exception sources. Table 4.2 lists the exception

sources and their vector addresses. Since the usable modes differ depending on the product, for

details on each product, refer to section 3, MCU Operating Modes.

Summary of Contents for H8S/2376 F-ZTAT

Page 24: ...Rev 1 0 09 01 page xxiv of xliv ...

Page 38: ...Rev 1 0 09 01 page xxxviii of xliv ...

Page 44: ...Rev 1 0 09 01 page xliv of xliv ...

Page 60: ...Rev 1 0 09 01 page 16 of 904 ...

Page 96: ...Rev 1 0 09 01 page 52 of 904 ...

Page 116: ...Rev 1 0 09 01 page 72 of 904 ...

Page 148: ...Rev 1 0 09 01 page 104 of 904 ...

Page 284: ...Rev 1 0 09 01 page 240 of 904 ...

Page 422: ...Rev 1 0 09 01 page 378 of 904 ...

Page 634: ...Rev 1 0 09 01 page 590 of 904 ...

Page 656: ...Rev 1 0 09 01 page 612 of 904 ...

Page 668: ...Rev 1 0 09 01 page 624 of 904 ...

Page 780: ...Rev 1 0 09 01 page 736 of 904 ...

Page 796: ...Rev 1 0 09 01 page 752 of 904 ...

Page 806: ...Rev 1 0 09 01 page 762 of 903 ...

Page 808: ...Rev 1 0 09 01 page 764 of 904 ...

Page 921: ...Rev 1 0 09 01 page 877 of 904 ø tBRQOD tBRQOD Figure 24 24 External Bus Request Output Timing ...

Page 938: ...Rev 1 0 09 01 page 894 of 904 ...