7 OSCILLATOR CIRCUIT (OSC)

66

EPSON

S1C17001 TECHNICAL MANUAL

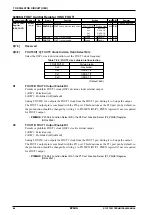

0x5061: Oscillation Control Register (OSC_CTL)

Register name Address

Bit

Name

Function

Setting

Init. R/W

Remarks

Oscillation

Control Register

(OSC_CTL)

0x5061

(8 bits)

D7–6

–

reserved

–

–

–

0 when being read.

D5–4

OSC3WT[1:0]

OSC3 wait cycle select

OSC3WT[1:0]

Wait cycle

0x0

R/W

0x3

0x2

0x1

0x0

128 cycles

256 cycles

512 cycles

1024 cycles

D3–2

–

reserved

–

–

–

0 when being read.

D1

OSC1EN

OSC1 enable

1 Enable

0 Disable

1

R/W

D0

OSC3EN

OSC3 enable

1 Enable

0 Disable

1

R/W

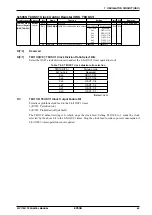

D[7:6] Reserved

D[5:4]

OSC3WT[1:0]: OSC3 Wait Cycle Select Bits

An oscillation stabilization wait timer is set to prevent malfunctions due to unstable clock operation at

the start of OSC3 oscillation.

The OSC3 clock is not fed to the system immediately after OSC3 oscillation starts—for example, when

power is first turned on, on awaking from SLEEP, or when the OSC3 oscillation circuit is turned on via

software—until the time set here has elapsed.

Table 7.8.2: OSC3 oscillation stabilization wait time settings

OSC3WT[1:0]

Oscillation stabilization

wait time

0x3

128 cycles

0x2

256 cycles

0x1

512 cycles

0x0

1,024 cycles

(Default: 0x0)

This is set to 1,024 cycles (OSC3 clock) after initial resetting. The CPU does not begin operating im-

mediately after resetting until this time has elapsed.

Note: The OSC3 oscillation start time depends on the oscillator and externally connected compo-

nents. The time should be set with an adequate oscillation stabilization wait time. Refer to the

typical oscillation start times specified in “24 Electrical Characteristics.”

D1

OSC1EN: OSC1 Enable Bit

Permits or prohibits OSC1 oscillator circuit operation.

1 (R/W): Permitted (on) (default)

0 (R/W): Prohibited (off)

Note: • The OSC1 oscillator circuit cannot be stopped if the OSC1 clock is being used as the sys-

tem clock.

• The OSC1 clock is not fed to the system for 256 cycles to prevent malfunctions immedi-

ately after OSC1 oscillation is started by changing the OSC1EN setting from 0 to 1.

D0

OSC3EN: OSC3 Enable Bit

Permits or prohibits OSC3 oscillator circuit operation.

1 (R/W): Permitted (on) (default)

0 (R/W): Prohibited (off)

Note: The OSC3 oscillator circuit cannot be stopped if the OSC3 clock is being used as the system

clock.

Summary of Contents for S1C17001

Page 1: ...Technical Manual S1C17001 CMOS 16 BIT SINGLE CHIP MICROCONTROLLER ...

Page 33: ...4 POWER SUPPLY VOLTAGE 24 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 63: ...6 INITERRUPT CONTROLLER 54 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 87: ...8 CLOCK GENERATOR CLG 78 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 91: ...9 PRESCALER PSC 82 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 133: ...11 16 BIT TIMER T16 124 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 211: ...16 STOPWATCH TIMER SWT 202 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 219: ...17 WATCHDOG TIMER WDT 210 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 241: ...18 UART 232 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 277: ...20 I2 C 268 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 313: ...25 PACKAGE 304 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...