6 INITERRUPT CONTROLLER

30

EPSON

S1C17001 TECHNICAL MANUAL

6.2 Vector Table

The vector table contains the vectors (processing routine start addresses) for interrupt processing routines. When

an interrupt occurs, the S1C17 core reads the vector corresponding to the interrupt and executes that processing

routine. The S1C17001 vector table starts from address 0x8000. The vector table base address can be read from the

TTBR register (0xffff80).

Table 6.2.1 shows the S1C17001 vector table.

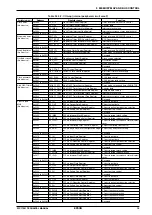

Table 6.2.1: Vector table

Vector No./ Soft-

ware interrupt No.

Vector address

Hardware interrupt name

Hardware interrupt factor

Priority

0 (0x00)

0x8000

Reset

• Low input to #RESET pin

• Watchdog timer overflow

*2

1

1 (0x01)

0x8004

Irregular address interrupt

Memory access command

2

–

(0xfffc00)

Debug interrupt

brk command etc.

3

2 (0x02)

0x8008

NMI

Watchdog timer overflow

*2

4

3 (0x03)

0x800c

reserved

–

–

4 (0x04)

0x8010

P0 port interrupt

P00 to P07 port input

High

*1

5 (0x05)

0x8014

P1 port interrupt

P10 to P17 port input

6 (0x06)

0x8018

Stopwatch timer interrupt

• Timer 100 Hz signal

• Timer 10 Hz signal

• Timer 1 Hz signal

7 (0x07)

0x801c

Clock timer interrupt

• Timer 32 Hz signal

• Timer 8 Hz signal

• Timer 2 Hz signal

• Timer 1 Hz signal

8 (0x08)

0x8020

8-bit OSC1 timer interrupt

Compare match

9 (0x09)

0x8024

reserved

–

10 (0x0a)

0x8028

11 (0x0b)

0x802c

PWM & capture timer interrupt

• Compare A

• Compare B

12 (0x0c)

0x8030

8-bit timer interrupt

Timer underflow

13 (0x0d)

0x8034

16-bit timer Ch.0 interrupt

Timer underflow

14 (0x0e)

0x8038

16-bit timer Ch.1 interrupt

Timer underflow

15 (0x0f)

0x803c

16-bit timer Ch.2 interrupt

Timer underflow

16 (0x10)

0x8040

UART interrupt

• Transmit buffer empty

• Receive buffer full

• Receive error

17 (0x11)

0x8044

Remote controller interrupt

• Data length counter underflow

• Input rising edge detection

• Input falling edge detection

18 (0x12)

0x8048

SPI interrupt

• Transmit buffer empty

• Receive buffer full

19 (0x13)

0x804c

I

2

C interrupt

• Transmit buffer empty

• Receive buffer full

20 (0x14)

0x8050

:

:

reserved

–

31 (0x1f)

0x807c

Low

*1

*1: When same interrupt level is set

*2: Watchdog timer interrupt selects reset or NMI using software.

Vector numbers 4 to 19 are assigned maskable interrupts supported by the S1C17001.

Summary of Contents for S1C17001

Page 1: ...Technical Manual S1C17001 CMOS 16 BIT SINGLE CHIP MICROCONTROLLER ...

Page 33: ...4 POWER SUPPLY VOLTAGE 24 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 63: ...6 INITERRUPT CONTROLLER 54 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 87: ...8 CLOCK GENERATOR CLG 78 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 91: ...9 PRESCALER PSC 82 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 133: ...11 16 BIT TIMER T16 124 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 211: ...16 STOPWATCH TIMER SWT 202 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 219: ...17 WATCHDOG TIMER WDT 210 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 241: ...18 UART 232 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 277: ...20 I2 C 268 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 313: ...25 PACKAGE 304 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...