18 UART

216

EPSON

S1C17001 TECHNICAL MANUAL

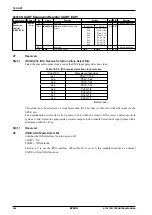

S1: Start bit, S2: Stop bit, P: Parity bit,

Wr: data writing to transmit data buffer

Sampling clock

SOUT

TDBE

TRBS

Interrupt

S1 D0 D1 D2 D3 D4 D5 D6 D7 P S2 S1 D0 D1

D7 P S2 S1 D0 D1

D7 P

Wr

Wr

Wr

S2

Figure 18.5.1: Data transmission timing chart

Data reception control

The receiving circuit is launched by setting the RXEN bit to 1, enabling data to be received from an external

serial device.

When the external serial device sends the start bit, the receiving circuit detects its Low level and starts sampling

the following data bits. The data bits are sampled at the sampling clock rising edge, and the lead bit is loaded

into the receive shift register as LSB. Once the MSB has been received into the shift register, the received data

is loaded into the receive data buffer. If parity checking is enabled, the receiving circuit checks parity at the

same time by checking the parity bit received immediately after the MSB.

The receive data buffer, a 2-byte FIFO, receives data until full.

Received data in the buffer can be read from the UART_RXD register (0x4102). The oldest data is read out

first, clearing the register.

∗

UART_RXD

: UART Receive Data Register (0x4102)

The receiving circuit includes the RDRY (D1/UART_ST register) and RD2B (D3/UART_ST register) buffer

status flags.

∗

RDRY

: Receive Data Ready Flag in the UART Status (UART_ST) Register (D1/0x4100)

∗

RD2B

: Second Byte Receive Flag in the UART Status (UART_ST) Register (D3/0x4100)

The RDRY flag indicates that the receive data buffer still contains data. The RD2B flag indicates that the re-

ceive data buffer is full.

(1) RDRY = 0, RD2B = 0

The receive data buffer contents need not be read, since no data has been received.

(2) RDRY = 1, RD2B = 0

One data item has been received. Read the receive data buffer contents once to clear the data inside the buf-

fer and reset the RDRY flag. The buffer reverts to state (1) above.

If the receive data buffer contents are read twice, the second data read will be invalid.

(3) RDRY = 1, RD2B = 1

Two data items have been received. Read the receive data buffer contents twice. The receive data buffer

outputs the oldest data first, clearing the buffer data read out and resetting the RD2B flag. The buffer then

reverts to the state in (2) above. The second read outputs the most recent received data, after which the buf-

fer reverts to the state in (1) above.

Even when the receive buffer is full, the shift register can receive one more item of data. An overrun error

will occur if additional data is sent from the external serial device in this state, and the new data will over-

write the shift register data. The contents of the receive data buffer must be read out before an overrun error

occurs. For detailed information on overrun errors, refer to Section 18.6.

The volume of data received can be checked by reading these flags.

Summary of Contents for S1C17001

Page 1: ...Technical Manual S1C17001 CMOS 16 BIT SINGLE CHIP MICROCONTROLLER ...

Page 33: ...4 POWER SUPPLY VOLTAGE 24 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 63: ...6 INITERRUPT CONTROLLER 54 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 87: ...8 CLOCK GENERATOR CLG 78 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 91: ...9 PRESCALER PSC 82 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 133: ...11 16 BIT TIMER T16 124 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 211: ...16 STOPWATCH TIMER SWT 202 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 219: ...17 WATCHDOG TIMER WDT 210 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 241: ...18 UART 232 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 277: ...20 I2 C 268 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 313: ...25 PACKAGE 304 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...