AD9361 Reference Manual

UG-570

| Page 99 of 128

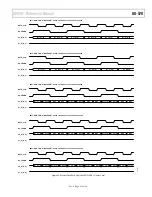

SINGLE PORT FDD FUNCTIONAL TIMING (CMOS)

The timing diagrams in Figure 68 and Figure 69 illustrate the relationship among the bus signals in single port FDD mode. Note that

because 2R1T and 1R2T systems follow the 2R2T timing diagrams, they are omitted from Figure 68 and Figure 69.

Figure 68. Receive Data Path, Single Port FDD

Figure 69. Transmit Data Path, Single Port FDD

DATA_CLK

RX_FRAME

P0_D[5:0]

P1_D[5:0]

R1_I[11:6]

R1_Q[11:6]

R1_I[5:0]

R1_I[5:0]

R1_I[11:6]

R1_Q[11:6]

R1_I[5:0]

R1_I[5:0]

R1_I[11:6]

R1_Q[11:6]

R1_I[5:0]

R1_I[5:0]

1R1T, DDR, FDD, SINGLE PORT, 0x010 = 0xC8, 0x011 = 0x00, 0x012 = 0x04

1

1668-

069

DATA_CLK

RX_FRAME

P0_D[5:0]

P1_D[5:0]

R1_I[11:6]

R1_Q[11:6]

R1_I[5:0]

R1_I[5:0]

R1_I[11:6]

R1_Q[11:6]

R1_I[5:0]

R1_I[5:0]

R1_I[11:6]

R1_Q[11:6]

R1_I[5:0]

R1_I[5:0]

2R2T, DDR, FDD, SINGLE PORT, 0x010 = 0xC8, 0x011 = 0x00, 0x012 = 0x04

FB_CLK

TX_FRAME

P0_D[11:6]

P1_D[11:6]

T1_I[11:6]

T1_Q[11:6]

T1_I[5:0]

T1_I[5:0]

T1_I[11:6]

T1_Q[11:6]

T1_I[5:0]

T1_I[5:0]

T1_I[11:6]

T1_Q[11:6]

T1_I[5:0]

T1_I[5:0]

1R1T, DDR, FDD, SINGLE PORT, 0x010 = 0xC8, 0x011 = 0x00, 0x012 = 0x04

1

1668-

070

FB_CLK

TX_FRAME

P0_D[11:6]

P1_D[11:6]

T1_I[11:6]

T1_Q[11:6]

T1_I[5:0]

T1_I[5:0]

T1_I[11:6]

T1_Q[11:6]

T1_I[5:0]

T1_I[5:0]

T1_I[11:6]

T1_Q[11:6]

T1_I[5:0]

T1_I[5:0]

2R2T, DDR, FDD, SINGLE PORT, 0x010 = 0xC8, 0x011 = 0x00, 0x012 = 0x04

0

0

Rev. A