UG-570

AD9361 Reference Manual

| Page 94 of 128

The data samples are carried in two’s complement format, with

D[11] as the numerically most significant bit and D[0] as the

least significant bit. In other words, the most positive sample

value is 0x7FF and the most negative value is 0x800. In this

mode, the I and Q data samples are time-interleaved on the data

bus. For a single RF path in each direction (a 1R1T system), the

I and Q samples are carried in a 2-way interleave:

I, Q, I, Q, …

For a system utilizing two Rx/Tx channels, the I and Q samples

from RF channels 1 and 2 are carried in a 4-way interleave:

I

1

, Q

1

, I

2

, Q

2

, I

1

, Q

1

, I

2

, Q

2

, …

For a system with a 2R1T or 1R2T configuration, the clock

frequencies, sample periods, and data capture timing are the

same as if configured for a 2R2T system. However, in the path

with only a single channel used, the disabled channel’s I-Q pair

in each data group is unused. These unused slots are ignored by

the

AD9361

. For example, in a 2R1T system with only Tx

Channel 1 used, the transmit burst would have two unused

slots, as follows:

I, Q, X, X, I, Q, X, X, …

The unused X slots may be filled with arbitrary data values by

the BBP. Such values can be fixed constant values, or the

preceding data sample values can be repeated to reduce the bus-

switching factor and; therefore, power consumption.

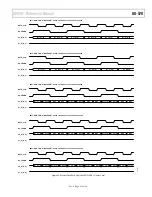

SINGLE PORT TDD FUNCTIONAL TIMING (CMOS)

The timing diagrams in Figure 65 and Figure 66 illustrate the

relationship among the bus signals in single port TDD mode.

These diagrams show an example of timing for both SDR and

DDR modes of operation. For all subsequent sections in this

section, only DDR timing will be shown. Figure 65 and

Figure 66 also include the timing diagrams for the 1R1T

scenario where the 2R2T Timing bit is set, forcing the data

transfer format to be the same as the 2R2T case. This mode is

useful for single port systems that may need to switch between

single channel and multichannel operation but cannot change

their data transfer format. The 2R2T bit has no effect if the

device is not configured 1R1T mode.

Note that the Tx_FRAME and Tx data must be transmitted

such that they meet the setup and hold requirements relative to

FB_CLK. In addition to the 1R1T and 2R2T scenarios, 1R2T

and 2R1T configurations are shown to illustrate that their

timing is identical to the 2R2T configuration. Behavior with

different combinations of receiver and transmitter channels in

other modes also follows the 2R2T timing behavior, so for all

subsequent sections these plots are omitted from the figures.

Rev. A