2-4

IM DLM3054-01EN

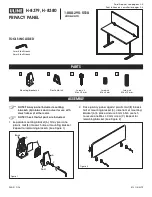

State Display (State)

The state display shows logic signal data that has been sampled on the edge of the signal specified as the clock

source. Even when the input signal changes, the state is retained until the clock source edge changes.

Display ON/OFF (State)

You can turn the state display on and off. If you turn it on, the state is shown according to the specified clock

source (Clock), detection level (Threshold), and clock source polarity (Polarity).

• ON: The state display is shown.

• OFF: The state display is hidden.

State Display Example

Clock source

(Polarity: )

State display

Input signal

Repetitive high-frequency pulse

Unknown area

Clock Source (Clock)

Select from the following.

CH1 to CH3, LOGIC (Bit0 to Bit7)

Clock Source Polarity (Polarity)

Select the clock source polarity.

When the clock source changes from low to high

When the clock source changes from high to low

When the clock source changes from low to high or from high to low

Detection Level (Threshold)

Set the level for detecting edges. Set this when the clock source is set to CH1 to CH3.

Range: ± 5 div

Hysteresis (Hysteresis)

You can apply a hysteresis to the detection level so that edges are not detected on small changes. Set this when

the clock source is set to CH1 to CH3.

Selectable range: 0.3 div to 8.0 div

Resolution: 0.1 div

• When the state display is ON, Math/Ref4 cannot be used.

• When the clock source is set to LOGIC, the source bit waveform is shown as-is.

2 Vertical Axis (Logic Signal)