www.ti.com

7.6.1

Selecting Bulk Capacitance

7.6.2

Recommended Capacitance

Power Supply

There are 2 factors that need to be considered when selecting the bulk capacitance: the effective ESR for

the power plane capacitors, and the amount of capacitance needed to provide power during periods when

the voltage regulator cannot respond.

The overall impedance of the core power plane is determined by:

(Allowable

Voltage

Deviation

due

to

Current

Transients)

/

(Max

Current)

In

Section 7.5

, it was suggested that the allowable voltage deviation allowed due to transient response is

18mV. The max transient current is estimated at 1.5A. So the impedance requirement is 18mV / 1.5Amps

= 12mohms. The power plane also has some impedance. An estimate of 2mohms will require a total

effective ESR of 10mohms. So the effective ESR of the bulk capacitors should not exceed this value.

Multiple bulk capacitors in parallel will help achieve this overall ESR.

The amount of the bulk capacitance is determined by the amount of time that the power regulator cannot

respond to the power demand and the amount of power that needs to be delivered during this time. The

maximum current change measurements have been made which show:

•

Max current swing: 1.5Amp

The decoupling caps provide the immediate current through the transition but the bulk capacitors need to

supply this current until the voltage regulator can respond. A typical power regulator would have about a

10KHz bandwidth with a large capacitive load (needed to maintain the 18mV deviation). Assuming this

bandwidth and a 1.5A current transient, the minimum bulk capacitance needed is estimated at 1500uF. So

for this case the bulk capacitance needs to add up to 1500uF and create an effective ESR of 10mohms.

The capacitance may need to be further increased to cover temperature derating. Examples of suitable

capacitors are shown in

Table 8

.

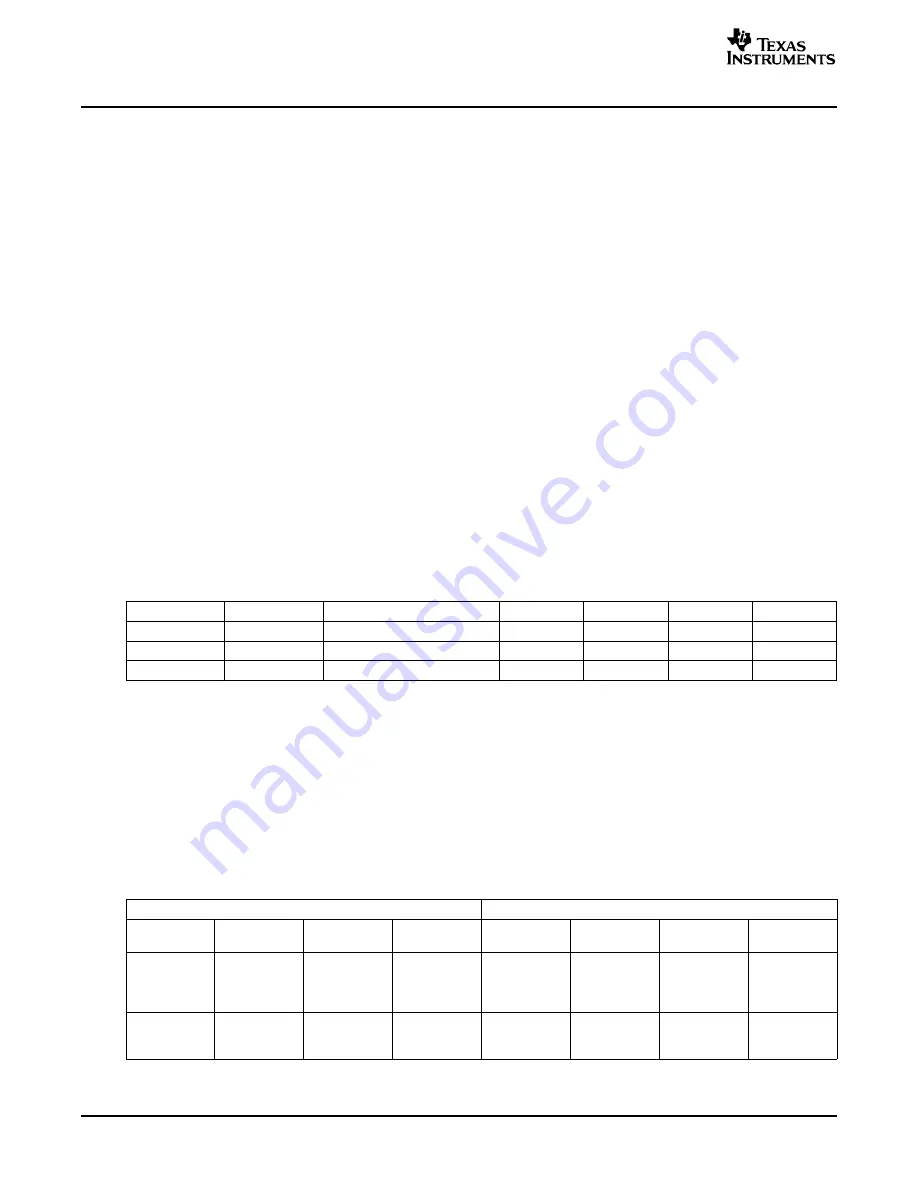

Table 8. Bulk Capacitor Examples

Manufacturer

Type

Part Number

C

Vmax

ESR

QTY

AVX

Tantalum

TPSD337K004R0035

330uF

4V

35m

Ω

5

KEMET

Tantalum

T530X687M004ASE005

680uF

4V

5m

Ω

3

SANYO

POS-CAP

2R5TPD1000M5

1000uF

2.5V

5m

Ω

2

Capacitor selection should be done as shown above for the specific power supply implementation. If

multiple TCI6482 devices are used on a single core power plane the total capacitance could be reduced

per device if the expectation was that the transients would not occur on all devices simultaneously.

Recommended capacitor selection is given in

Table 9

where it is also compared with the TCI100 capacitor

recommendations. The TCI6482 capacitor selection does not necessarily include power supply output

capacitance. Output capacitors are provided along with the power supply reference designs.

Table 9. Capacitor Recommendations

TCI6482

TCI100

Voltage

Capacitors

Total

Description

Voltage

Capacitors

Total

Description

Supply

Capacitance

Supply

Capacitance

CVDD

10 * 560pF

2084uF

1.2V Core

CVDD

1 * 330uF

333.2 uF

Core

20 * 100nF

32 * 100nF

3 * 680uF

2 * 22uF

DVDD33

16 * 560pF

330uF

3.3V I/O

DVDD

1 * 330uF

333.2 uF

I/O

24 * 100nF

32 * 100nF

1 * 330uF

20

TMS320TCI6482 Design Guide and Migration from TMS320TCI100

SPRAAC7B – April 2006

Submit Documentation Feedback