Hardware-Based Protection

24

SLUUBD3D – September 2015 – Revised September 2018

Copyright © 2015–2018, Texas Instruments Incorporated

Protections

3.6

Hardware-Based Protection

The bq78350-R1 device has two main hardware-based protections, AOLD and ASCD, with adjustable

current and delay time. Setting

ASCD Threshold and Delay [RSNS]

doubles the threshold value. It is

located in bit 8 of the

ASCD Threshold Delay

register. The

Threshold

settings are in mV; therefore, the

actual current that triggers the protection is based on the R

SENSE

used in the schematic design.

For details on how to configure the AFE hardware protection, refer to the tables in the companion data

manual,

bq769x0 3-Series to 15-Series Cell Battery Monitor Family for Li-Ion and Phosphate Applications

(

).

All of the hardware-based protections provide a short term Trip/Alert/Recovery protection to account for a

current spike as well as a Trip/Alert/Latch protection for persistent faulty condition. The latch feature also

stops the FETs from toggling on and off continuously, preventing damage to the FETs.

In general, when a fault is detected after the

Delay

time, the DSG FET will be disabled. However, if

Protection Configuration [LPEN]

is set, then both FETs are turned off (Trip stage), and an internal fault

counter will be incremented (Alert stage). As the DSG FET is turned off, the current will drop to 0 mA.

After

Recovery

time, the CHG and DSG FETs will be turned on again (Recovery stage) unless additional

recovery conditions are enabled.

If the alert is caused by a current spike, the fault count will be decremented after

Counter Dec Delay

time. If this is a persistent faulty condition, the device will enter the Trip stage after

Delay

time, and repeat

the Trip/Alert/Recovery cycle. The internal fault counter is incremented every time the device goes through

the Trip/Alert/Recovery cycle. Once the internal fault counter hits the

Latch Limit

, the protection enters a

Latch stage and the fault will only be cleared through the Latch Reset condition. If Latch Limit is set to 0, it

will latch after the first detection.

The Trip/Alert/Recovery/Latch stages are documented in each of the following hardware-based protection

sections.

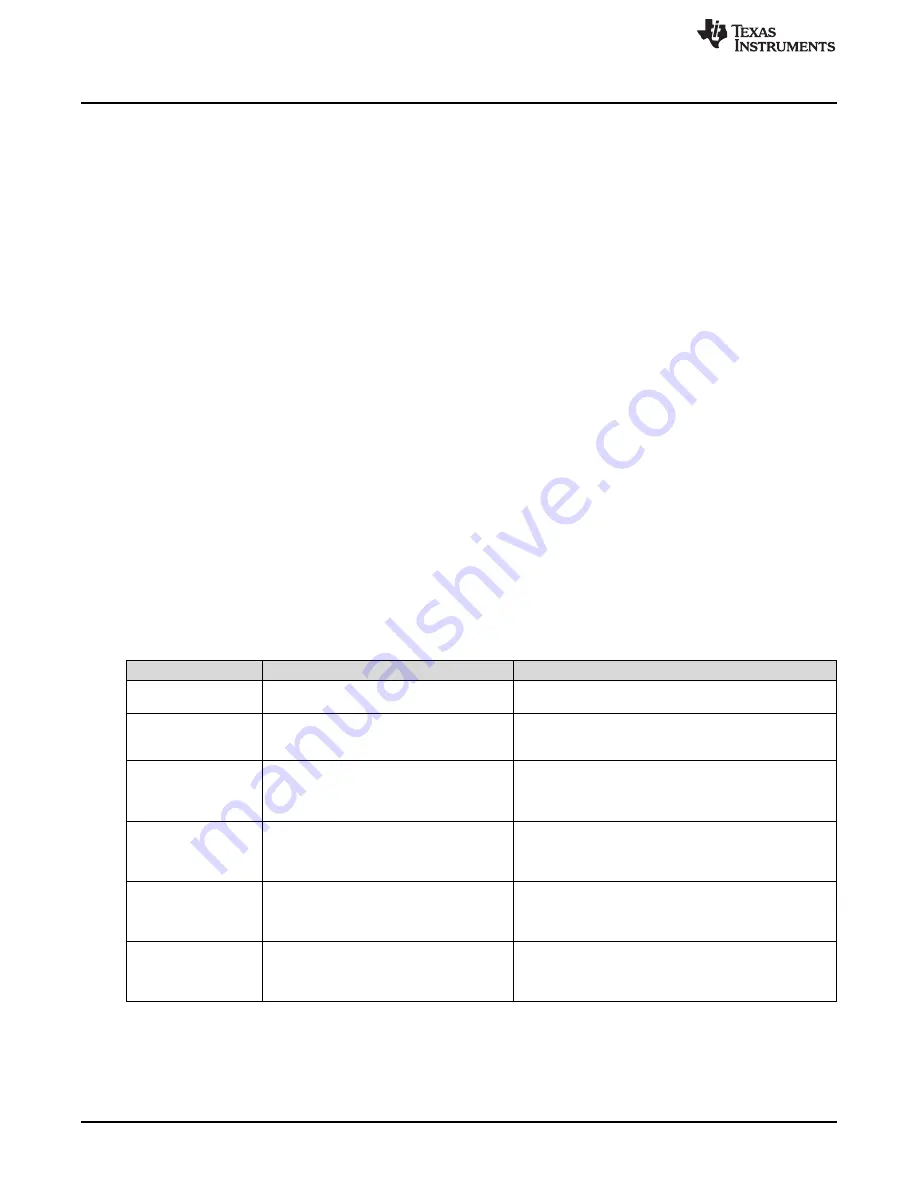

3.6.1 Overload in Discharge Protection

The device has a hardware-based overload in discharge protection with adjustable current and delay. See

for additional FET action options.

Status

Condition

Action

Normal

Current()

> (

AOLD Threshold and

Delay[3:0]

/R

SENSE

)

SafetyAlert()[AOLDL]

= 0, if AOLDL counter = 0

Alert

AOLDL counter > 0

SafetyAlert()[AOLDL]

= 1

Decrement AOLDL counter by one after each

AOLD:Counter Dec Delay

period

Trip

Current()

continuous

≤

(

AOLD Threshold

and Delay[3:0]

/R

SENSE

) for

AOLD Threshold

and Delay[6:4]

duration

SafetyStatus()[AOLD]

= 1

OperationStatus()[XDSG]

= 1

DSG FET is disabled.

Increment AOLDL counter

Latch

AOLDL counter

≥

AOLD:Latch Limit

SafetyAlert()[AOLDL]

= 0

SafetyStatus()[AOLDL]

= 1

OperationStatus()[XDSG]

= 1

DSG FET is disabled.

Recovery

SafetyStatus()[AOLD]

= 1 for

AOLD:Recovery

time OR

If

Protection Configuration [LPEN]

= 1

AND

AFEStatus()[LOAD_PRESENT]

= 0

SafetyStatus()[AOLD]

= 0

OperationStatus()[XDSG]

= 0

DSG FET returns to normal if

SafetyStatus[AOLDL]

= 0.

Latch Reset

SafetyStatus()[AOLDL]

= 1

for A

OLD:Reset

time

SafetyStatus()[AOLDL]

= 0

Reset AOLDL counter

OperationStatus()[XDSG]

= 0

DSG FET returns to normal if

SafetyStatus()[AOLD]

= 0.