Rev.6.00 Oct.28.2004 page 647

of 1016

REJ09B0138-0600H

19.21

Interrupt Handling when Programming/Erasing Flash Memory

All interrupts, including NMI input, are disabled when flash memory is being programmed or erased (when the P or E bit

is set in FLMCR1), and while the boot program is executing in boot mode*

1

, to give priority to the program or erase

operation. There are three reasons for this:

1. Interrupt during programming or erasing might cause a violation of the programming or erasing algorithm, with the

result that normal operation could not be assured.

2. In the interrupt exception handling sequence during programming or erasing, the vector would not be read correctly*

2

,

possibly resulting in MCU runaway.

3. If an interrupt occurred during boot program execution, it would not be possible to execute the normal boot mode

sequence.

For these reasons, in on-board programming mode alone there are conditions for disabling interrupts, as an exception to

the general rule. However, this provision does not guarantee normal erasing and programming or MCU operation. All

interrupt requests, including NMI, must therefore be restricted inside and outside the MCU when programming or erasing

flash memory. The NMI interrupt is also disabled in the error-protection state while the P or E bit remains set in FLMCR1.

Notes: 1. Interrupt requests must be disabled inside and outside the MCU until the programming control program has

completed programming.

2. The vector may not be read correctly in this case for the following two reasons:

• If flash memory is read while being programmed or erased (while the P or E bit is set in FLMCR1), correct

read data will not be obtained (undetermined values will be returned).

• If the interrupt entry in the vector table has not been programmed yet, interrupt exception handling will not

be executed correctly.

19.22

Flash Memory Programmer Mode

19.22.1

Programmer Mode Setting

Programs and data can be written and erased in programmer mode as well as in the on-board programming modes. In

programmer mode, the on-chip ROM can be freely programmed using a PROM programmer that supports the Renesas

Technology microcomputer device type with 256-kbyte on-chip flash memory (FZTAT256V5A). Flash memory read

mode, auto-program mode, auto-erase mode, and status read mode are supported with this device type. In auto-program

mode, auto-erase mode, and status read mode, a status polling procedure is used, and in status read mode, detailed internal

signals are output after execution of an auto-program or auto-erase operation.

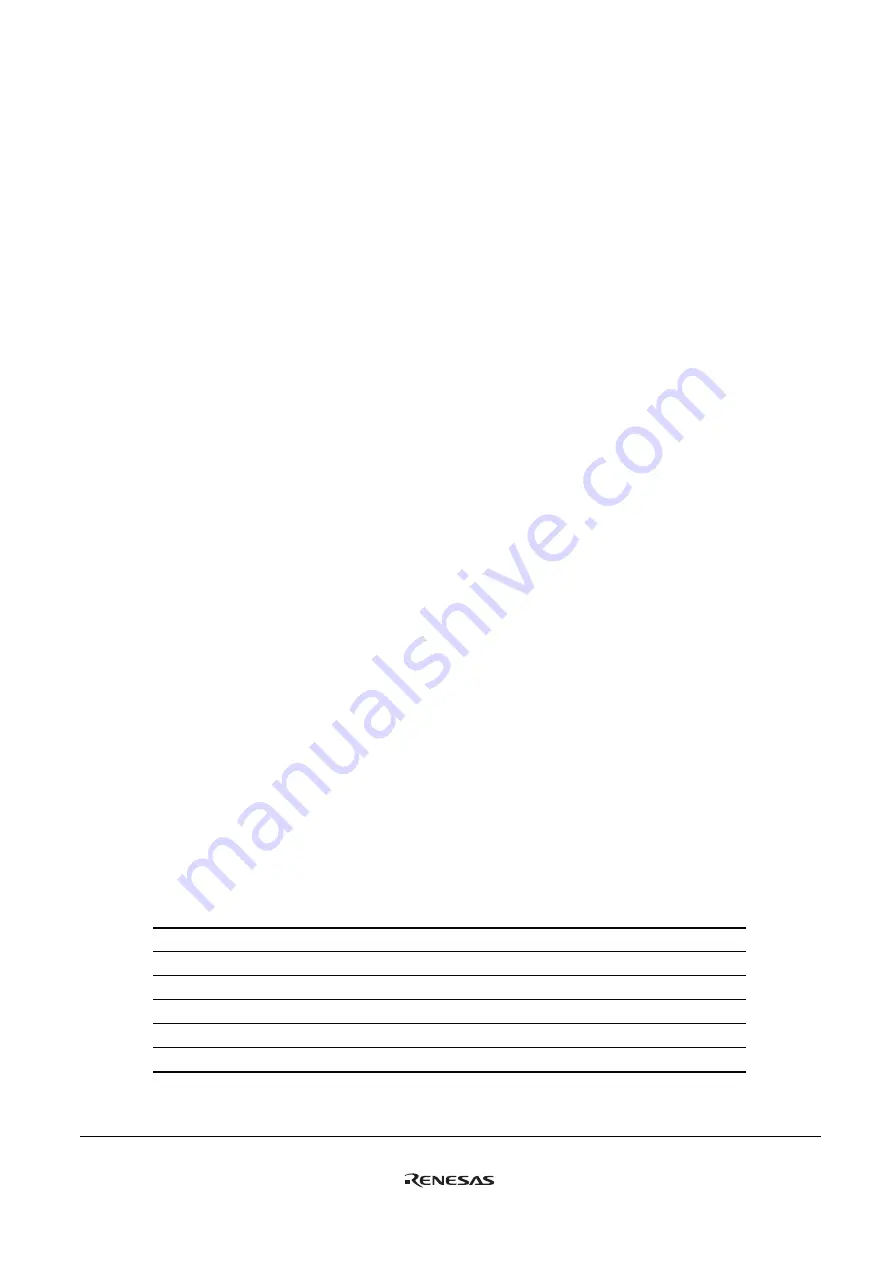

Table 19-39 shows programmer mode pin settings.

Table 19-39 Programmer Mode Pin Settings

Pin Names

Settings/External Circuit Connection

Mode pins: MD2, MD1, MD0

Low-level input

Mode setting pins: P66, P65, P64

High-level input to P66, low-level input to P65 and P64

STBY

pin

High-level input (do not select hardware standby mode)

RES

pin

Reset circuit

XTAL, EXTAL pins

Oscillator circuit

Other pins requiring setting: P32, P25

High-level input to P32, low-level input to P25

Содержание ZTAT H8S/2357F

Страница 4: ......

Страница 28: ...Rev 6 00 Oct 28 2004 page xxiv of xxiv REJ09B0138 0600H...

Страница 82: ...Rev 6 00 Oct 28 2004 page 54 of 1016 REJ09B0138 0600H...

Страница 108: ...Rev 6 00 Oct 28 2004 page 80 of 1016 REJ09B0138 0600H...

Страница 364: ...Rev 6 00 Oct 28 2004 page 336 of 1016 REJ09B0138 0600H...

Страница 438: ...Rev 6 00 Oct 28 2004 page 410 of 1016 REJ09B0138 0600H...

Страница 566: ...Rev 6 00 Oct 28 2004 page 538 of 1016 REJ09B0138 0600H...

Страница 588: ...Rev 6 00 Oct 28 2004 page 560 of 1016 REJ09B0138 0600H...

Страница 688: ...Rev 6 00 Oct 28 2004 page 660 of 1016 REJ09B0138 0600H...

Страница 694: ...Rev 6 00 Oct 28 2004 page 666 of 1016 REJ09B0138 0600H...

Страница 708: ...Rev 6 00 Oct 28 2004 page 680 of 1016 REJ09B0138 0600H...

Страница 1044: ...Rev 6 00 Oct 28 2004 page 1016 of 1016 REJ09B0138 0600H...

Страница 1047: ...H8S 2357 Group H8S 2357F ZTATTM H8S 2398F ZTATTM Hardware Manual 2 6 2 Ote machi Chiyoda ku Tokyo 100 0004 Japan...