Rev.6.00 Oct.28.2004 page 475

of 1016

REJ09B0138-0600H

For details of clock source selection, see table 14-9 in section 14.3, Operation.

Bit 1

CKE1

Bit 0

CKE0

Description

0

0

Asynchronous mode

Internal clock/SCK pin functions as I/O port

*

1

Clocked synchronous

mode

Internal clock/SCK pin functions as serial clock

output

1

Asynchronous mode

Internal clock/SCK pin functions as clock output

*

2

Clocked synchronous

mode

Internal clock/SCK pin functions as serial clock

output

1

0

Asynchronous mode

External clock/SCK pin functions as clock input

*

3

Clocked synchronous

mode

External clock/SCK pin functions as serial clock

input

1

Asynchronous mode

External clock/SCK pin functions as clock input

*

3

Clocked synchronous

mode

External clock/SCK pin functions as serial clock

input

Notes: 1. Initial value

2. Outputs a clock of the same frequency as the bit rate.

3. Inputs a clock with a frequency 16 times the bit rate.

14.2.7

Serial Status Register (SSR)

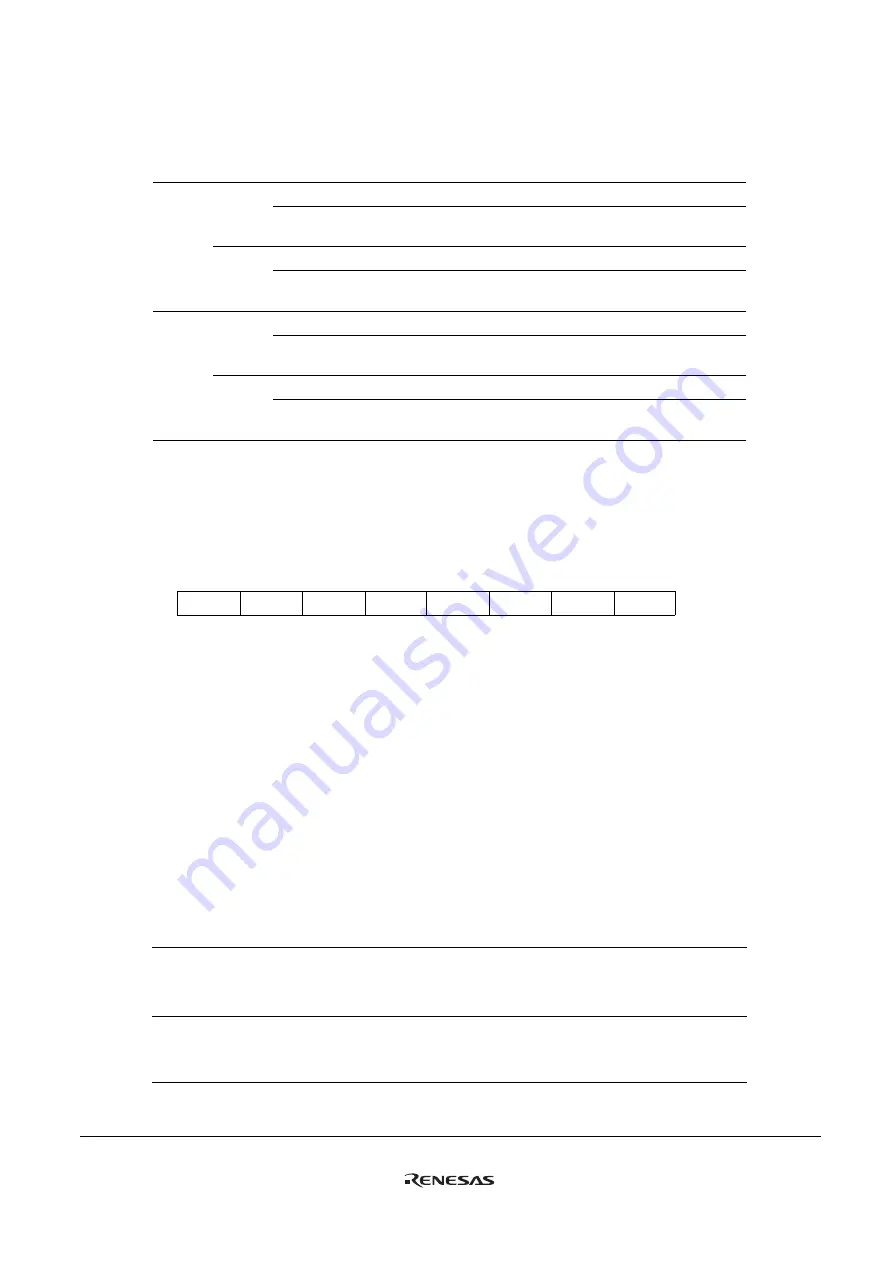

Bit

:

7

6

5

4

3

2

1

0

TDRE

RDRF

ORER

FER

PER

TEND

MPB

MPBT

Initial value :

1

0

0

0

0

1

0

0

R/W

:

R/(W)

*

R/(W)

*

R/(W)

*

R/(W)

*

R/(W)

*

R

R

R/W

Note:

*

Only 0 can be written, to clear the flag.

SSR is an 8-bit register containing status flags that indicate the operating status of the SCI, and multiprocessor bits.

SSR can be read or written to by the CPU at all times. However, 1 cannot be written to flags TDRE, RDRF, ORER, PER,

and FER. Also note that in order to clear these flags they must be read as 1 beforehand. The TEND flag and MPB flag are

read-only flags and cannot be modified.

SSR is initialized to H'84 by a reset, and by putting the device in standby mode or module stop mode.

Bit 7—Transmit Data Register Empty (TDRE): Indicates that data has been transferred from TDR to TSR and the next

serial data can be written to TDR.

Bit 7

TDRE

Description

0

[Clearing conditions]

•

When 0 is written to TDRE after reading TDRE = 1

•

When the DMAC or DTC is activated by a TXI interrupt and write data to TDR

1

[Setting conditions]

(Initial value)

•

When the TE bit in SCR is 0

•

When data is transferred from TDR to TSR and data can be written to TDR

Содержание ZTAT H8S/2357F

Страница 4: ......

Страница 28: ...Rev 6 00 Oct 28 2004 page xxiv of xxiv REJ09B0138 0600H...

Страница 82: ...Rev 6 00 Oct 28 2004 page 54 of 1016 REJ09B0138 0600H...

Страница 108: ...Rev 6 00 Oct 28 2004 page 80 of 1016 REJ09B0138 0600H...

Страница 364: ...Rev 6 00 Oct 28 2004 page 336 of 1016 REJ09B0138 0600H...

Страница 438: ...Rev 6 00 Oct 28 2004 page 410 of 1016 REJ09B0138 0600H...

Страница 566: ...Rev 6 00 Oct 28 2004 page 538 of 1016 REJ09B0138 0600H...

Страница 588: ...Rev 6 00 Oct 28 2004 page 560 of 1016 REJ09B0138 0600H...

Страница 688: ...Rev 6 00 Oct 28 2004 page 660 of 1016 REJ09B0138 0600H...

Страница 694: ...Rev 6 00 Oct 28 2004 page 666 of 1016 REJ09B0138 0600H...

Страница 708: ...Rev 6 00 Oct 28 2004 page 680 of 1016 REJ09B0138 0600H...

Страница 1044: ...Rev 6 00 Oct 28 2004 page 1016 of 1016 REJ09B0138 0600H...

Страница 1047: ...H8S 2357 Group H8S 2357F ZTATTM H8S 2398F ZTATTM Hardware Manual 2 6 2 Ote machi Chiyoda ku Tokyo 100 0004 Japan...